基于PC104 總線的實時信號采集處理系統(tǒng)

0 引言

PC104是嵌入式工控機的一種,其外部總線接口為PC104 總線.使用堆疊的方式可以將多個PC104 主板結(jié)合到一起,并通過螺栓固定,保證系統(tǒng)的牢固可靠,應(yīng)對惡劣的使用環(huán)境.由于PC104具有功耗低,體積小,擴展性高,功能強大等優(yōu)點,其已經(jīng)在航空航天.軍用武器裝備.工業(yè)控制等領(lǐng)域得到了廣泛的使用.

在對武器裝備進行測試維護時,經(jīng)常需要對設(shè)備中的各類模擬信號進行分析,從而對武器系統(tǒng)的運行情況做出判斷.目前常見的測試設(shè)備往往實時性不高,無法更多地進行人機交互.同時由于測試設(shè)備體積過于龐大,并不方便在外場對武器裝備進行直接的測試和維護.隨著現(xiàn)階段軍用裝備外場測試的信息化程度逐漸提高,迫切需要研制出體積小.結(jié)構(gòu)緊湊的便攜式實時測試設(shè)備.

目前主流的實時信號采集方式是通過高速A/D 轉(zhuǎn)換器件來完成的,其優(yōu)點是信號精度高,實時的信號采集帶來了大量的數(shù)據(jù)需要處理,對后端的信號處理系統(tǒng)提出了較高的要求.因此本文搭建了基于PC104總線的實時信號采集處理系統(tǒng),憑借FPGA的高速處理能力控制A/D轉(zhuǎn)換器完成數(shù)據(jù)的采集,并通過PC104總線將數(shù)據(jù)提供給上位機完成用戶對實時信號的監(jiān)測.

1 總體設(shè)計方案

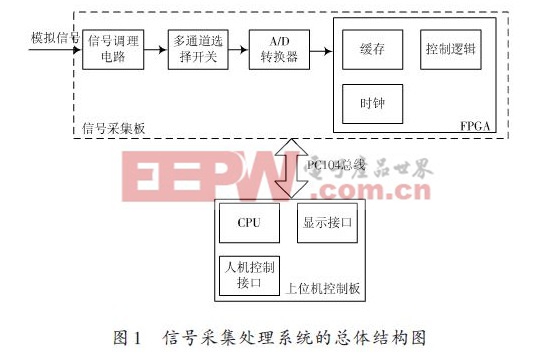

本文的實時信號采集處理系統(tǒng)主要包括信號采集板和上位機控制板2部分,兩者之間通過PC104總線進行通信.上位機控制板以CPU 為核心,擴展出VGA,RJ45等人機交互所需要的外圍設(shè)備接口.信號采集板主要包括了FPGA 邏輯控制.A/D 轉(zhuǎn)換器.通道選擇開關(guān).前端信號調(diào)理器等.實時信號采集處理系統(tǒng)的總體結(jié)構(gòu)圖如圖1所示.

信號采集處理系統(tǒng)進行工作時,上位機控制板的CPU通過PC104總線向底層信號采集板發(fā)送命令,對其工作參數(shù)進行設(shè)置.CPU 與FPGA 之間通過地址和數(shù)據(jù)總線完成命令及數(shù)據(jù)的交互.多通道選擇開關(guān)對外部輸入的模擬信號進行通道選擇,在信號調(diào)理芯片對模擬信號進行相應(yīng)的預(yù)處理之后,在FPGA的邏輯控制下由A/D轉(zhuǎn)換器完成信號的采集.FPGA通過PC104總線實時地將采集的信號數(shù)據(jù)傳輸給CPU,通過運行在上位機控制板的應(yīng)用程序完成數(shù)據(jù)的最終分析和處理.信號采集處理系統(tǒng)可以通過FPGA 邏輯控制模塊靈活地調(diào)整采樣速率,來滿足多種信號不同速率的采樣要求.

2 硬件系統(tǒng)設(shè)計

2.1 上位機控制板

本系統(tǒng)采用深圳盛博公司的PC104 模塊SCM9022作為上位機控制系統(tǒng)硬件平臺,其處理器為英特爾凌動N455 處理器,使用了1 GB 的DDR3 內(nèi)存,支持2 GB 的SSD 和1 路SATA 接口,支持2 個100 Base-T 以太網(wǎng)口,具有8路GPIO接口和6個串口,4個USB 2.0接口,標準鼠標鍵盤接口,支持18 位的LVDS 和VGA 顯示.

SCM9022的硬件資源可以滿足對所需要采集信號的處理,用戶可以方便地使用其通用的外設(shè)接口完成必要的人機交互.上位機控制板包括了64 針腳的雙排單列插針J1 和40 針腳的雙排單列插針J2,總共104 根信號總線.上位機控制板是標準的PC104模塊,其尺寸為96 mm×90 mm?當(dāng)工作在8 b數(shù)據(jù)模式下時,J2的針腳信號無效,只有J1針腳有效;當(dāng)工作在16 b數(shù)據(jù)模式下時,J1和J2所有針腳都有效.在104個針腳中,包括了16個數(shù)據(jù)針腳,7個鎖存地址針腳,20個地址針腳,32個控制針腳,14 個地線和電源線,1 個14 MHz 的OSC,1 個8 MHz 的BCLK?其中,SA[011]為地址總線;SD[07]為數(shù)據(jù)總線;IOR 為輸入/輸出接口的讀控制,低電平有效;IOW 為輸入/輸出接口的寫控制,低電平有效;DATA 為串行數(shù)據(jù);BALE 為地址鎖存信號;CLK 為移位脈沖;SY-CLK 為總線時鐘;IOCHADY 為輸入/輸出接口的準備就緒信號,該信號由集電極開路門或三態(tài)門驅(qū)動,低電平時處于無效狀態(tài),表示輸入/輸出接口設(shè)備需要將總線的周期延長.時序如圖2所示.

2.2 信號采集板

為了能快速高效保證上位機控制板與信號采集板之間的PC104總線數(shù)據(jù)通信,底層的信號采集板使用了Altera公司的Cyclone Ⅲ系列FPGA芯片EP3C25F256C7N,通過控制邏輯來按照PC104總線的時序進行數(shù)據(jù)傳輸.該芯片具有200 Kb邏輯單元.8 Mb嵌入式存儲器以及396個嵌入式乘法器能夠在控制信號采集芯片的同時,將采集的信號數(shù)據(jù)傳輸給上位機.需要注意的是,由于PC104總線的針腳都是5 V電平,而FPGA芯片采用了3.3 V的電平信號,所以在信號采集板上使用了74LVH162245芯片對電平進行轉(zhuǎn)換,調(diào)整電氣特性,完成由TTL電平向LVTTL電平的轉(zhuǎn)換,并增強驅(qū)動能力.在信號的采集過程中,由于外部的多路模擬輸入信號往往比較微弱,其電平的幅度很小,為了保證A/D轉(zhuǎn)換模塊采集到足夠強的信號幅度,在信號采集板中使用了放大器INA103把輸入信號進行調(diào)理放大到0~10 V之間.INA103是由BB公司生產(chǎn)的低功率增益可調(diào)通用儀器放大器,其具有高精度寬帶寬的特點.在增益為100時,對應(yīng)的帶寬仍達到200 kHz?該芯片采用了可調(diào)電阻調(diào)整放大倍數(shù),具體公式如式(1)所示:

本系統(tǒng)在信號采集板中采用了R = 6 Ω,故得到的放大倍數(shù)在0~1001 之間,保證了該芯片輸出給A/D 轉(zhuǎn)換器的信號電平在0~10 V之間.信號采集板的多路選擇開關(guān)采用了AD 公司的ADG508A 八選一高速選通開關(guān).系統(tǒng)通過2 片ADG508A 并行控制模擬信號的輸入,實現(xiàn)了對16路信號的實時采集.多路開關(guān)的輸入通斷是通過控制使能引腳EN以及CH0,CH1,CH2來完成的,F(xiàn)PGA 輸出的地址的最高位分別接到2 片ADG508A 的使能端,地址低3 位分別接入ADG508A 的A0,A1,A2?信號采集板的A/D 轉(zhuǎn)換芯片采用了BB 公司的ADS7805,其具有高速.低功耗的特點.在5 V 的工作電壓下其最高的轉(zhuǎn)換頻率達到了100 kHz?該芯片內(nèi)部自帶有時鐘.電壓基準和采樣保持等電路,極大的簡化了用戶的電路設(shè)計,并且提高了系統(tǒng)的穩(wěn)定性.

模擬信號相關(guān)文章:什么是模擬信號

評論