如何在FPGA和ASIC設計中結合高速USB功能

SIE IP的主要功能是要執行數據編碼和解碼,CRC生成和錯誤校驗,位填充,數據包ID生成,串到并以及并到串轉換。這個IP可以自己開發或者可以從第三方供應商購買。FPGA也要執行上層USB協議。外部要使用一個收發器IC,比如賽普拉斯的TX2UL收發器芯片。這款收發器是USB 2.0認證的符合收發器紅單元接口(UTMI)相關標準。所需的所有終端,包括Dplus 線上的1.5 K歐姆的上拉電阻,都是在芯片里內置了。

該方法的優點是所需外部硬件最少。使用這種方法的缺點是開發復雜的USB堆棧IP需要時間以及工程資源。SIE IP執行,上層協議和應用功能也占用了FPGA的大量資源。使用第三方的IP成本會很昂貴。

使用集成SIE和收發器芯片的USB橋

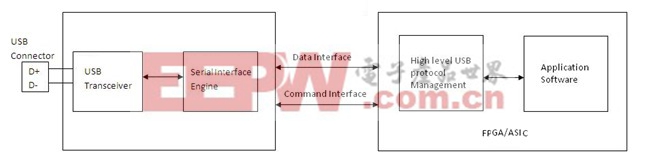

另一種把USB接口整合到FPGA設計的方式是連接一個外部串行接口引擎IC和收發器(見圖4)。

圖4. FPGA +橋芯片(SIE+ PHY)

在這里,FPGA只需要實現上層USB協議。任何從USB主設備收到的命令都會通過SIE傳遞到FPGA.FPGA需要包含邏輯來對這些命令進行恰當的響應。例如,在枚舉過程中,USB外設會

從主設備得到一個命令,請求它的描述符。在這個實現中,外部硬件,即收發器和SIE,會收到封包,并通過一個中斷通知FPGA命令已收到。FPGA就會在STE讀寄存器,并了解到外設已收到來自主設備的GET描述符命令。它會把正確的描述符發送給SIE.和使用外部收發器的SIE IC 不同,USB橋芯片如賽普拉斯的Mobl-USB芯片內置了SIE以及收發器。該控制器有兩個雙緩高速端點,其共享2 KB FIFO空間,最大化了靈活度和吞吐量,還有控制端點0.

這種實現的最大好處是,減少了FPGA一半的復雜性(例如,信號級協議管理)。然而,即使在這種情況下,還要占用一定數量的FPGA資源來執行上層USB協議。在這種情況下,需要做的決定是,要分析要分析所需外部硬件成本 vs. 節省的FPGA資源。

使用USB控制器與FPGA

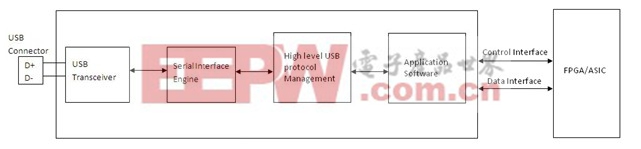

圖5. USB控制器+ FPGA

最后一種方式是,連接全功能 USB控制器到FPGA(見圖5)。在這種情況下,所有的USB協議管理都會發生在FPGA以外。專門的USB控制器IC包含PHY,SIE,協議控制邏輯。

控制器可以提供靈活的端點可配置數量,FIFO大小,甚至可能包含一個微控制器來處理上層USB協議管理。這種外設控制器可以處理一些應用功能,從而不再需要FPGA或ASIC處理這些事務。如果他們包含RAM架構,開發人員還可以進行靈活的現場固件升級。

現在FPGA只需要掌握和這個芯片的邏輯接口。USB控制器和FPGA之間的接口可以是任何的標準接口,例如SPI,I2C,或HPI.還可能是自定義的接口,這在USB控制器IC中很普遍。

賽普拉斯的FX2LP 是專門的外設控制器芯片,其可以減少將USB集成到FPGA或ASIC系統的開發時間。它包含了一個簡單的"從FIFO"接口,使得和FPGA系統互聯很簡單。從FIFO接口功能具備從讀和從寫信號,可以讀或寫數據到FX2LP 4 K FIFO空間。

對于與ASIC系統互聯,FX2LP包含一個GPIF或通用可編程接口邏輯接口,可以為ASIC處理或通訊的任何標準接口生成接口波形。GPIF還可以通過USB接口配置FPGA,這樣就不需要一個單獨的配置芯片,例如PROM或處理器。通過USB配置FPGA也不再需要JTAG.因此,通用的專用的USB控制器可以不僅僅作為一個數據通道,還可以減少線路板尺寸和成本。

這篇文章里提到的這三種設計方法都有自己的優點和缺點。選擇時要進行仔細分析,要權衡成本,線路板空間,和FPGA資源。

評論