一種嵌入式USB2.0主機控制器IP核的研究與設計

2. 2 配置寄存器

配置寄存器主要分為兩種: 狀態寄存器和控制寄存器。為了提高代碼可讀性, 設計中定義了5 個32 位寄存器: USB 命令寄存器; 端口狀態寄存器;USB 信息包域A 寄存器; USB 信息包域B 寄存器;傳輸狀態寄存器。 這些寄存器分別寄存數據傳輸中的一些控制命令, 傳輸狀態, 端口狀態改變情況以及傳輸數據包特性等。

2. 2. 1 DMA 控制器

本設計將DMA 控制器設計為兩種工作模式:

DMA master 模式和DMA slave 模式。 采用一個模式選擇信號來選擇DMA 工作模式, 如下:

此選擇信號值由配置寄存器配置, 當總線沒有外部DMA 控制器控制時, USB 主機中DMA 控制器選擇工作在master 模式, 在這種模式中, 當USB主機有數據傳輸的需求時, DMA 控制器向CPU 發起請求, CPU 將對DMA 控制器配置數據傳輸的起始地址, 數據傳輸總大小, 傳輸數據包大小等信息,并釋放總線給DMA 控制器接管, 此時DMA 控制器完全接管對總線的控制, USB 主機與存儲器之間數據傳輸不經過CPU, 而直接交換USB 主機外部存儲器和USB 主機內數據緩沖器之間數據。 當數據傳輸結束后DMA 控制器通知CPU 重新接管總線。

DMA master 模式一般用于高速地傳送成組的數據。

DMA mater 模式的主要優點是速度快。 由于整個數據傳輸過程不需要CPU 干預, 因此就省去了CPU操作時間, 減少了CPU 工作負擔, 減小了對CPU 的要求, 很大程度的降低成本。 當總線有外部DMA 控制器接管時, USB 主機中DMA 控制器工作在slave模式, 此時USB 主機內DMA 控制器模塊不起作用, USB 主機與外部存儲器之間數據傳輸必須經過CPU 來啟動外部DMA 來搬運外部存儲器和USB主機內數據緩沖器中的數據, 這樣就加大了CPU 工作量, 對CPU 要求也相應的提高, 數據傳輸速度也有所下降。

2. 2. 2 數據緩沖器

數據緩沖器模塊用來緩沖從設備端輸入的數據和CPU 端要輸出的數據。 本設計采用乒乓緩沖buffer0, buffer1, 在讀buffer0 數據的同時在向buffer1 里寫入下一個數據, 然后讀buffer1 的數據并寫數據到buffer0, 這樣交替讀寫數據, 很大程度的提高了數據傳輸速度。 在IN 傳輸中, 將從設備端輸入的數據寫入數據緩沖器中, 數據寫完后會發起一個中斷信號通知CPU 來取出其中的數據, 同樣在OUT 傳輸中, 將從CPU 過來的數據寫入數據緩沖器中, 隨后將寫入的數據傳輸到設備端。

2. 2. 3 根集線器及PIE

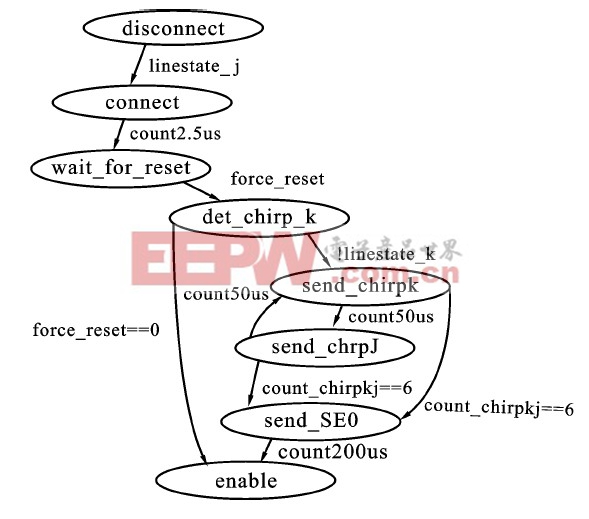

根集線器其實也是一種特殊的設備, 它下游端口還可以繼續串聯其他集線器, 最終能夠為127 個USB 設備提供連接端口, 根集線器主要任務是管理連接到根集線器上的設備以及負責設備與主機之間的數據通信。 設計中通過圖3 的狀態機來實現根集線器對設備的枚舉過程。

圖3 枚舉狀態機

有高速能力的設備在第一次連接到USB 總線時必須使用全速。 而后, 該設備在總線重置階段中向根集線器發送一個Chirp K, 如上游的集線器支持高速速率, 則應答一個Chirp K 與Chirp J 交替序列,這樣高速集線器和高速設備都使用高速傳輸速率通信, 如根集線器不支持高速速率, 則忽略高速設備發送的Chirp K, 即不應答ChirpK 與Chirp J 交替序列。 這樣高速設備必須維持在全速模式。

PIE 模塊在設計中實現對傳輸的信息包處理,如包拆分, 包封裝等。 其內部設計的子模塊有crc. v,pid decoder. v, pid encoder. v, rec packet. v,trans packet. v, timeout. v 等等。 實現傳輸信息包中pid 的編碼, 譯碼以及對pid 的檢錯等功能, 同時還包括對信息包的crc 檢測及對數據傳輸過程中超時的檢測。

3 系統驗證環境

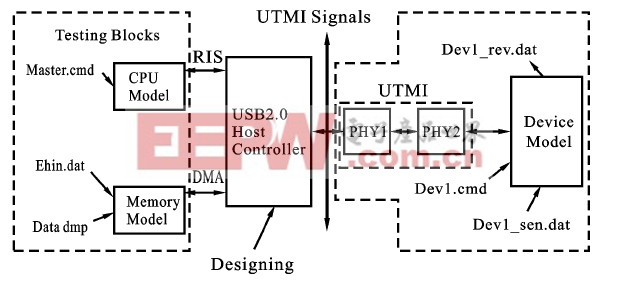

為了驗證嵌入式USB2. 0 主機控制器, USB 接口用了PHY 模型和設備模型, 總線接口采用CPU和存儲器模型, 如圖4 所示, 外部CPU 和存儲器有兩個通道與嵌入式USB 主機作用: 寄存器通道和DMA通道。 CPU 通過寄存器通道來讀寫嵌入式USB 主機中配置寄存器中數據, 而DMA 通道主要用來交換存儲器模型與嵌入式USB 主機中數據緩沖器中數據。

圖4 嵌入式USB2. 0 主機控制器仿真環境

評論