一種高速USB設(shè)備控制器IP核的設(shè)計與實現(xiàn)

1 引言

為了滿足各種不同設(shè)備類型需求,USB2.0 規(guī)范在USB1.1 全速(12Mbps)及低速(1.5Mbps)的基礎(chǔ)上增加了高速(480Mbps)傳輸速率,同時為了兼容USB1.x 規(guī)范,高速設(shè)備在全速信號環(huán)境中必須以全速正常工作,即能夠在高/全速兩種信號環(huán)境中正確地進行速率切換,這也加大了高速設(shè)備控制器的設(shè)計難度。本文通過分析USB2.0 協(xié)議, 利用VerilogHDL 實現(xiàn)了符合該規(guī)范的高速設(shè)備控制器IP 核,同時對設(shè)計中的幾個問題加以討論并提出相應(yīng)的解決方案。

2 USB2.0 協(xié)議

包(Packet)是USB 傳輸?shù)淖钚挝弧C總€數(shù)據(jù)包的開始都有同步頭(SYNC)以及相應(yīng)的包標示符(PID),包的結(jié)尾處都有包結(jié)束符(EOP)。在全/低速信號環(huán)境中,SYNC 長度為8 個時鐘周期(對應(yīng)一個字節(jié)01h),EOP 為2 個時鐘周期的單端0 (singleend,SE0)。而在高速信號環(huán)境中,除了新添加了幾個信息包PID,以及同步頭、EOP 分別增加到4 個字節(jié)長度和1 個字節(jié)(有個例外, 就是SOF 后面的EOP 可以到4 字節(jié))長度以外,為保證包中數(shù)據(jù)的正確性而進行的PID 互補校驗以及數(shù)據(jù)字段的CRC 校驗都沒有變化。

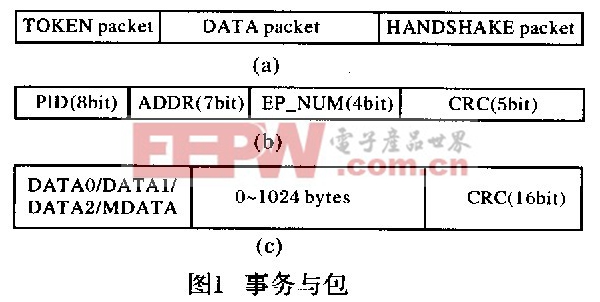

USB 傳輸(Transfer)是通過一個或者多個包含一系列數(shù)據(jù)包的事務(wù)(transaction)完成的,事務(wù)的格式示意圖如圖1(a)所示。令牌數(shù)據(jù)包定義傳輸類型、目標設(shè)備地址、端點號碼以及數(shù)據(jù)傳輸方向,如圖1(b);數(shù)據(jù)階段的數(shù)據(jù)包裝載長度與傳輸類型相關(guān)的數(shù)據(jù),如圖1(c);握手應(yīng)答包(在同步傳輸中沒有)定義該次事務(wù)的結(jié)果, 視接收情況分為4 種:ACK、NAK、STALL、NYET,分別表示數(shù)據(jù)成功接受、設(shè)備忙、設(shè)備(端點)不可用、還沒有足夠的緩存空間接受下一個數(shù)據(jù)包。

每一個USB 設(shè)備的端點都有其特定的屬性標明如何訪問它,每一種傳輸類型也都和具體的應(yīng)用要求相聯(lián)系。為了支持各種設(shè)備類型,USB 規(guī)范提供中斷(interrupt) 傳輸、塊(bulk) 傳輸和同步(isochronous) 傳輸以滿足不同的應(yīng)用要求。控制(control)傳輸基本用于主機(HOST)對設(shè)備進行配置以及下達各種命令,且有專門的PID 標示。因高速環(huán)境中總線帶寬大大的提升,所以包的數(shù)據(jù)字段的有效載荷都相應(yīng)的加大了。不過對于任何高速設(shè)備來說,首先都是以全速設(shè)備出現(xiàn),如果其復(fù)位時發(fā)出握手信號(線性調(diào)頻脈沖)主機端應(yīng)答成功,則斷開上拉電阻而進入高速模式。

3 設(shè)備控制器核的設(shè)計與實現(xiàn)

3.1 設(shè)計思想

目前USB 設(shè)備端控制器的實現(xiàn)主要有兩種方式:一是全集成芯片,如專用的微處理器(MCU)內(nèi)嵌符合USB 規(guī)范的SIE(Serial Interface Engine);二是部分集成芯片,如分立的通用微處理器+SIE。前者涉及到要開發(fā)專用的MCU,開發(fā)時間長、風(fēng)險大;后者集成度雖低,但不需專門設(shè)計MCU,極大地縮短了開發(fā)時間和風(fēng)險性,同時應(yīng)用時具有更大靈活性。考慮設(shè)計開發(fā)時間、設(shè)計工作量及應(yīng)用測試等因素,本設(shè)計采用第二種方式(外置通用MCU),完成設(shè)備控制器整個數(shù)字部分IP 核的設(shè)計。

設(shè)計完成的IP 核實現(xiàn)了控制,中斷,批量,同步四種模式傳輸,同時根據(jù)總線信號環(huán)境自動完成高/全速轉(zhuǎn)換。為了降低MCU 的開發(fā)難度,精簡內(nèi)部的中斷產(chǎn)生, 自動實現(xiàn)數(shù)據(jù)重傳而不需要MCU 的任何干預(yù)。

3.2 模塊劃分及具體實現(xiàn)

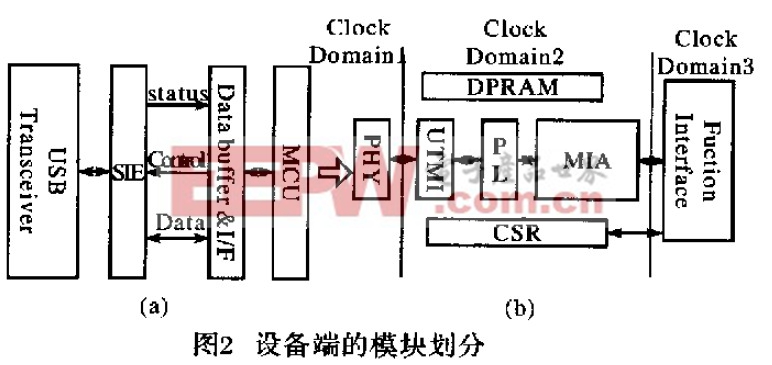

該USB 設(shè)備控制器的邏輯功能框圖如圖2(a)所示。SIE(串行接口引擎)為該設(shè)計的核心。設(shè)備在接收數(shù)據(jù)時, 對NRZI 數(shù)據(jù)流進行解碼并提交數(shù)據(jù)及其接收情況;發(fā)送數(shù)據(jù)時生成相應(yīng)的數(shù)據(jù)PID 并進行NRZI 編碼發(fā)送出去。為了更好地實現(xiàn)整個控制邏輯,把整個設(shè)備端控制器核劃成6 大塊:物理層PHY,收發(fā)器宏單元接口UTMI,協(xié)議層PL,存儲接口仲裁MIA , 內(nèi)部狀態(tài)控制寄存器CSR 以及端點存儲DPRAM,如圖2(b)所示。

3.2.1 PHY

由USB2.0 協(xié)議規(guī)范可知, 高速設(shè)備控制器必須能在高/全速信號環(huán)境之間正確切換, 因此PHY必須能夠根據(jù)工作模式確定其信號環(huán)境;其次必須進行高速480M/全速12 MHz 的NRZI 數(shù)據(jù)流解碼、編碼工作及其相應(yīng)的串并、并串轉(zhuǎn)換。設(shè)計中PHY使用了Philips 的ISP1501, 因此該部分數(shù)模混合設(shè)計不做介紹,ISP1501 的詳情請參考文獻。

3.2.2 UTMI

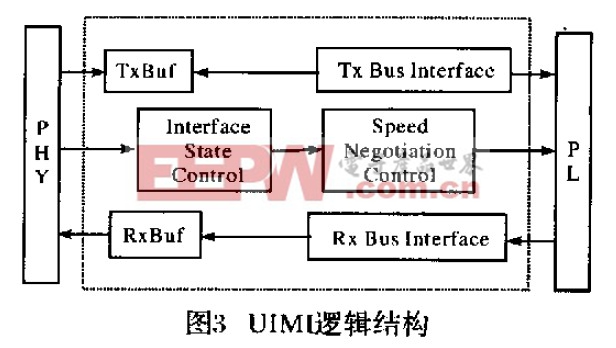

UTMI 控制suspend/resume 的產(chǎn)生以及生成全/高速之間切換的模式信號, 由于ISP1501 的數(shù)據(jù)線寬度為16 bits,一次處理一個字(1 word=2 bytes),故還要起到PHY 與協(xié)議層(PL)之間數(shù)據(jù)交換的緩沖作用。內(nèi)部框架如圖3 所示。速度協(xié)商控制(SNC)為該模塊的核心。

評論