一種高速USB設備控制器IP核的設計與實現

3.2.3 PL

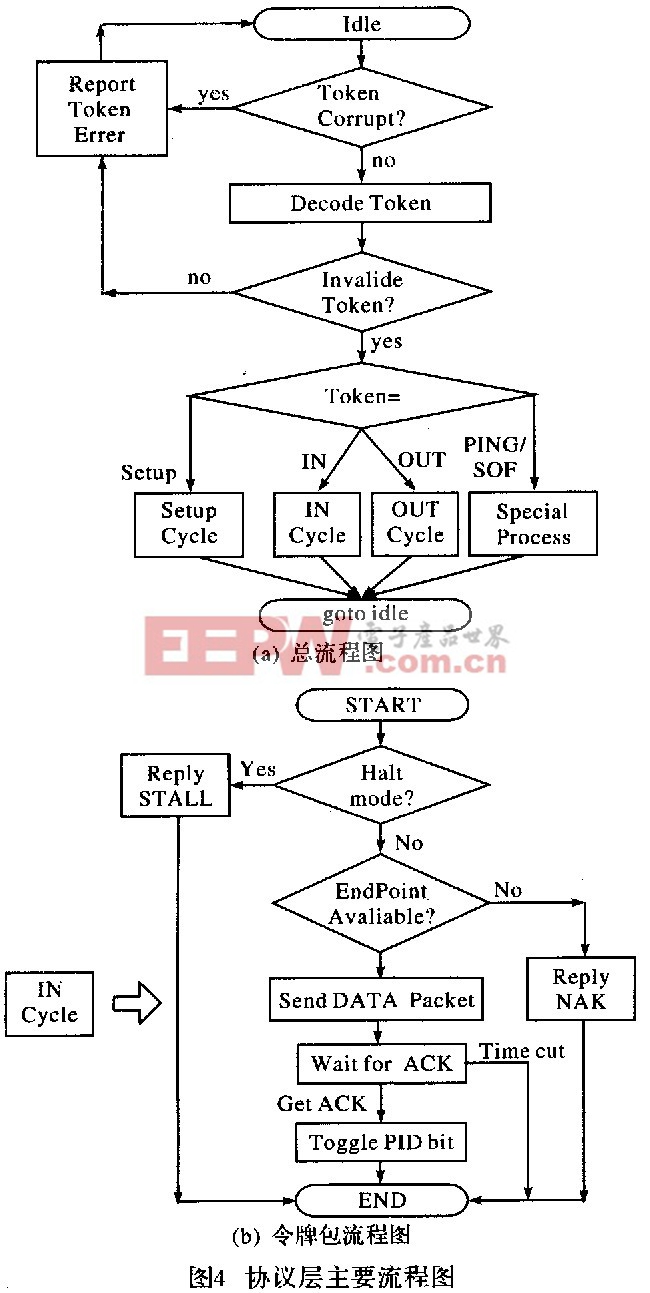

協議層模塊是整個SIE 的核心,控制著整個數據傳輸。總流程圖如圖4(a)所示。該過程主要有兩個步驟:第一,檢查PID 的有效性;第二,如果PID 有效,則根據PID 確定數據及傳輸類型。因此該模塊實際上是4 個進程處理:IN、OUT、SETUP 事務以及特殊事務。在具體的模塊設計實現中, 由于解包(Packet disassemble)、打包(Packet assemble)過程在4 個進程中都必不可少,所以統一編寫而在PL 頂層調用。內部狀態機的翻轉以及復位都是以事務為周期,所以實現起來比較容易。在接收數據時,解析出各種令牌以及把數據包的內容寫入RAM 中, 完畢以后填寫相應的接收信息。發送數據時,從RAM 中讀取數據并形成正確的數據PID。如果是0 長度的數據,則只有2 個字節的全0 CRC16 校驗碼。在一個事務的握手(handshake)階段,則根據接收情況提交握手信號。圖4(b)中給出了一個PID 為IN 令牌包的流程。

在USB 規范中,PID 為SETUP 標志的控制傳輸也稱作消息(Message)傳輸,其實際上可以理解成為一種特殊的OUT 傳輸, 主要用來對USB 設備的配置以及向設備發送和數據傳輸相關的命令字。有著固定的格式:以PID[3:0]=1101 的SETUP 令牌包開始的建立階段+數據階段+狀態階段。數據階段可以沒有, 如HOST 給設備下放地址時的控制傳輸,但是狀態階段是必需的,以確保傳輸的正確性。

3.2.4 MIA

存儲接口仲裁。存儲管理設計的好壞直接影響控制器整體性能,需要謹慎處理。對存儲單元進行讀、寫操作者是HOST 與MCU 兩者。設計中要注意的是MCU 的讀寫信號與內部時鐘的同步問題,這在后面部分還會進一步討論。

3.2.5 DPRAM 與CSR

DPRAM 暫存傳輸中事務的數據, 同時把該次事務的接收狀態信息寫入對應的CSR(狀態控制寄存器)。本設計把DPRAM 配置成端點FIFO,共16個, 總容量為8K。MCU 的工作是基于中斷的,當SIE 給出中斷時,首先會讀出相應端點的CSR 從而知道中斷產生的原因以及上次事務的狀態:成功或失敗。若失敗則進入相應的中斷例行程序。

3.3 設計中若干問題及其解決

3.3.1 端點的存儲管理單元(MMU)

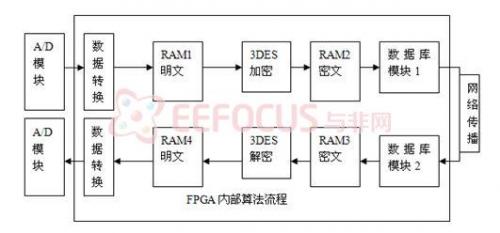

在USB1.x 規范中,由于數據有效載荷較小,純粹意義上的FIFO, 由于不需尋址即可實現存取操作、邏輯控制簡單等原因而作為端點的最好實現方法。但在USB2.0 規范中,由于帶寬、吞吐量劇增,且FIFO 不便動態配置等原因, 故端點存儲選擇RAM來實現。無論在FPGA 設計還是ASIC 設計中,都可使用兩種類型的RAM:單口(single port)RAM 與雙口(dual port)RAM。對于雙口RAM,其特別之處在于可同時讀寫, 即HOST 與MCU 可以同時對同一個端點進行讀寫操作。比如在由HOST 到設備方向的高速同步傳輸中,如果使用SPRAM 的話,同步端點的深度至少應配置為1024 (除非使用雙緩沖)且必須等到端點"Full"然后才產生中斷讓MCU 讀取端點內的數據。因此為了實現同步傳輸,SPRAM 配置實現的話,為了節省存儲單元而一般需要雙緩沖機制, 但增加了端點讀寫控制的復雜性; 而雙口RAM 由于能夠同時對不同地址的存儲單元進行讀寫(如果同時讀寫相同地址的話,則看RAM 具體的時序了),因此雙口RAM 只需要很少的緩沖存儲容量就可以滿足了, 為了使MCU 能夠及時地讀取數據,同時,又不致對MCU 的中斷過于頻繁,只要在寫入到端點深度的一半處產生中斷信號即可。因此設計中采用DPRAM,既可節省存儲資源(減小了芯片面積),又可提高同步傳輸的"實時同步"性。

3.3.2 異步時鐘域之間的數據交互

從前面的功能劃分可以看到,整個USB 設備控制器分成3 個不同的時鐘域。時域1 和時域2 之間實際上是同步的, 因為PHY 為時域2 提供了與數據同步的30MHz 的時鐘,所以這里的異步時鐘域主要是指時域2 與時域3 之間, 這在SIE 與MCU 之間的讀寫信號很容易看到。由于MCU 發出的最小讀寫有效脈寬比時域2 內的時鐘周期要小很多,比如在本設計中最小讀寫脈寬為15ns,而內部的時鐘為30MHz(T=33.3ns)。當MCU 要讀取數據時,可以采用"超前送數"策略,即根據MCU 的讀寫命令字在讀有效信號來之前把數據放入三態數據輸出端口的輸入端, 用讀有效電平作為三態的開關即可。

MCU 讀完本次數據以后,SIE 內部的異步讀寫控制邏輯立即對內部的MMU 產生一個讀請求(如果還沒有讀空),準備好下一個數據。整個MMU 收到的讀寫信號是由異步讀寫控制邏輯內部產生的,對MCU 接口透明, 該方法在FPGA 驗證中實現通過。

上述異步讀寫控制邏輯的設計是基于8051 類MCU的,值得注意的是,若MCU 是wishbone SoC 總線規范兼容的接口, 則不需上述復雜的讀寫控制邏輯,在這兩個時鐘域之間交換數據時,為了解決亞穩態問題,只須增加一級由本地時鐘觸發的寄存器實現作為過渡即可。

3.3.3 傳輸中一些錯誤檢測及其處理

為了精簡MCU 的編程,設計中提出"在保證傳輸正確的基礎上盡量減少中斷" 的設計原則。

USB2.0 規范中列出了種類繁多的錯誤產生及其相應的檢測、恢復方法。筆者認為,USB 設備控制器設計者沒有必要對傳輸過程中發生的任何錯誤都向外部MCU 提出中斷,對規范中部分類型的錯誤,設備控制器內部應有處理及恢復機制。例如超時的發生有幾種情形:正確接受完畢來自HOST 的非同步數據包后,必須及時返回一個成功接收握手;HOST發出IN 令牌包接收到數據以后, 同樣必須及時地返回握手包,否則超時。對后者,沒有必要馬上向MCU 產生中斷, 下一個IN 令牌到來時自動重傳上次數據, 且最多嘗試3 次。若問題依舊, 再中斷MCU,說明設備上游的線路可能出了故障。另一個就是Toggle 同步機制, 出錯也完全沒有必要通知MCU,可在協議實現的內部來處理。值得一提的是,控制傳輸比較特殊:在控制傳輸的建立階段,SETUP令牌包后面的數據包的PID 一定是DATA0,然后在這個基礎上進行觸發切換。在狀態階段的數據包PID 肯定是DATA1。否則,在FPGA 驗證中,即使觸發位出錯,主機還是會返回ACK,造成數據已正常接收的假象,而實際上主機已摒棄了數據。

4 系統仿真及FPGA驗證

在設計的編碼過程中,先分別對各模塊進行了功能仿真,子模塊仿真正確后對整個模塊進行了整體功能仿真,然后綜合代碼、設置引腳、自動布局布線后下載到FPGA 內。本設計FPGA 器件采用Altera 的ACEX1K EP1K100QC208-3。USB 電纜的一端接在測試板的transceiver 上, 另一端接至PC機的USB 接口上,如果SIE 邏輯功能正確,則Windows會識別出一個新的USB 設備, 完成了PnP 過程。為了功能驗證和應用測試,額外編寫了一個模塊,用于USB 設備枚舉時,模擬MCU 的部分功能。

Windows 在對USB 設備進行枚舉時,按如下順序進行:

(1) 主機發出一個復位信號;

(2) 初次得到設備描述符的控制傳輸;

(3) 給設備分配地址。數據包DATA0 的第三個Byte 就是分配的地址;

(4) 以新的地址獲取設備描述符;

(5) 初次獲取設備配置描述符,以確定配置描述符+接口描述符+端點描述符的長度,這次主機只獲取9 個字節的配置描述符。

(6) 獲取字符串描述符(可能沒有),根據設備描述符中是否有STRING 索引而定;

(7) 獲取完整的設備配置描述符,一次性獲取相應長度的上述三個描述符。

若以上步驟都正確, 則主機發現新的USB 設備,要為該設備安裝驅動程序。然后利用Windriver可以在Windows 環境看到這個USB 設備以及相關端點信息等資源。在該驅動程序的控制臺上,可以對USB 設備控制器的管道進行讀寫操作,并且報告操作結果,以驗證核的功能是否正確。

5 結束語

系統邏輯功能仿真、綜合后門級網表(gate levelnetlist) 功能仿真以及最后的FPGA 驗證都表明:本設計中,雙口RAM 配置、異步時鐘域之間讀寫時的"超前送數策略"以及"盡可能減少錯誤中斷產生"原則,簡化了編碼實現以及外部MCU 編程,在實現高速USB 設備控制器的設計過程中是有效的、切實可行的。該方案實現的USB2.0 設備控制器IP 核便于修改、易于實現,既可以進一步完成ASIC 設計,也可作為一個功能模塊嵌入到SOC 中。

參考文獻:

[1].bulkdatasheethttp://www.dzsc.com/datasheet/bulk_2523104.html.

[2].ISP1501 datasheethttp://www.dzsc.com/datasheet/ISP1501+_1083529.html.

評論