轉向使用即插即用的分層 DFT 的好處

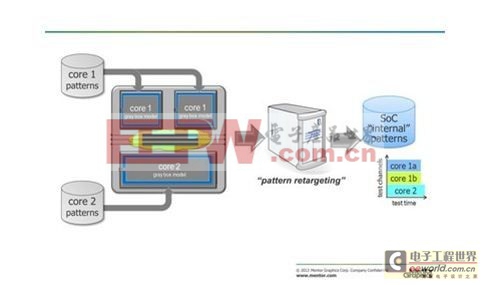

五、將內核測試圖案重定向并整合到頂層

分層 DFT 方法可以便捷地實現頂層IC的測試圖案整合。第一步是執行一些基本的DFT設計規則檢查(DRC)。完成這一步只需要有頂層網表和所有內核的灰盒模型(圖3)。分層DFT方法常常使用IC 層測試訪問機制(TAM),將芯片的IO定向到需要測試的特殊區塊或區塊組。它既可以簡單到只需要幾個多路復用器,也可以復雜得多。復用的內核通常有并聯廣播到所有內核的輸入信道,這樣從一套輸入信道就得到同樣的測試。我們比較建議將TAM建立在 IJTAG 的基礎上,因為IJTAG是一個非常廣泛而靈活的標準,也最適用于即插即用。

圖3:模式重定向需要獨立生成的內核測試圖案,并對其進行重新定向,使之可以從IC層執行。這張圖顯示了被重定向并整合的三個內核測試圖案,使其并行執行。對于一個典型的 IC來講,會有一些區塊的測試圖案被整合,而另一部分區塊需要被放到另一階段進行測試。

分層方法的最后一步是生成測試各內核之間互連的IC層測試圖案。灰盒模型在這里被應用。它是設計后期的 ATPG 步驟,因為所有內核設計和 TAM 首先必須在此之前完成。

六、下一步是什么?

分層 DFT的掃描和包裝器插入、灰盒生成和測試圖案重定向等基本特性為許多設計提供了一個顯著優勢。但是選擇哪些模塊并行測試,哪些串行測試,使測試效率得到優化還需要很多做很多工作。有效的頂層規劃要求一些內核測試圖案信息必須是有效的。與幫助確定最佳壓縮配置的壓縮分析的功能類似,頂層TAM規劃在內核設計可用時更為高效。針對這個問題正在開發的方法之一是將IC信道帶寬動態分配給各個內核。這樣的話,在設計TAM前就不需要知道內核測試圖案的性質。此外,動態分配掃描信道將減少整個測試圖案集的大小。

七、報告總結

分層DFT方法正在被許多設計所采用,它顯著加快了 ATPG 的速度,降低了工作站的規模。這對于數億門或以上的超大規模設計來說至關重要。分層DFT 的另一大優點是它很大程度上改進了工序,帶來了即插即用的便利。因此,只要內核設計完成,那么更多的DFT和 ATPG 工作可以在設計周期的更早階段進行,這些都有利于降低風險、提高可預見性、以及后期的 ECO。

評論