轉向使用即插即用的分層 DFT 的好處

一、背景

傳統的全芯片 ATPG 正日漸衰退,對于許多現有的和未來的集成芯片器件來說,一項主要挑戰就是如何為龐大數量的設計創建測試圖案。對于有百萬門甚至數億門的設計,傳統上等到設計完成再創建測試圖案的方法是不切實際的,產生所有這些圖案需要龐大的計算能力和相當多的時間。分層可測試性設計通過在區塊或內核上完成了 DFT 插入和圖案生成解決了這個問題。這大大減少了圖案生成時間和所需的計算資源。它還能讓你在設計過程中提前完成大部分 DFT 和圖案生成,從而大幅提高可預測性并降低風險。本文將介紹分層 DFT 流程的:插入掃描包裝器 (Wrapper)、為內核生成灰盒圖像,將內核級圖案重定向到集成芯片頂層的簡單映射步驟。

二、為什么即插即用是合理的?

即插即用這種方法帶來的一個重要好處就是,在設計過程中你可以在內核層面提前完成所有工作。這降低了許多類型的風險,因為任何問題都可以提前解決,讓最終芯片測試架構和結果變得更可預見。在內核層面做更多的測試工作還能讓各單獨的開發團隊獨立工作,然后向做芯片集成工作的同事交付標準的 DFT 操作和測試圖案等數據。此外,一旦設計和圖案數據完成,同樣的數據可以被重新用于任何使用該內核的芯片設計。即插即用方法同樣非常靈活。如果設計出現問題,需要進行工程更改(ECO),那么只需要對進行ECO的內核重新生成測試圖案。

三、使用包裝器鏈打造獨立內核

分層和內核的即插即用方法的基本要求之一是,確保每個內核可以獨立進行測試。DFT 工具可以從內核IO開始,并橫穿內核邏輯直到找到第一個寄存器,然后將其包括在包裝器鏈中。這些單元由于同時執行功能性任務和測試任務,因而被稱為共享包裝器單元。許多設計包含寄存器IO,這樣進出內核的信號的時序能得到很好地確定。這使包裝器插入變得非常簡單。

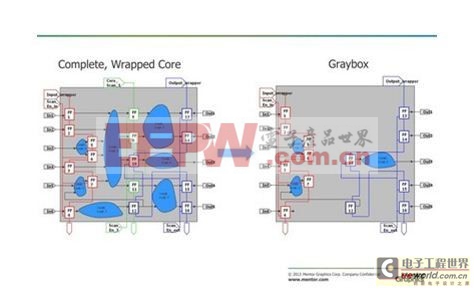

包裝器鏈同時還支持頂層IC建模和規則檢查。一旦包裝器鏈被插入,DFT 工具程序可以分析任何內核,并找出IO和包裝器鏈之間存在什么樣的邏輯。利用該邏輯,內核的部分圖像被寫出,我們稱之為灰盒(圖1)。灰盒被用來驗證內核在頂層的連接是否正確(設計規則檢查),同時也被用來創建各種內核之間的簡單互連測試。

圖1:當掃描鏈插入內核,包裝器鏈的結構允許將內核隔離為一個完整的包裝器內核,如左圖所示。右圖顯示了一個灰盒模型,其中頂層測試只需要內核IO和包裝器鏈之間的邏輯。

四、內核層面的模式生成

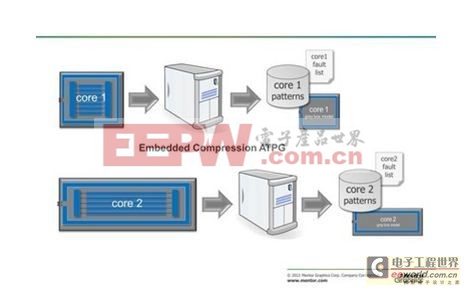

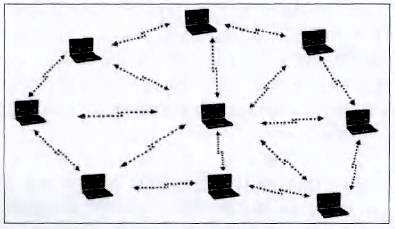

分層DFT的優點是,內核DFT和 ATPG 的進行能夠完全獨立于其他內核(圖2)。即便 IO 值未知,包裝器鏈也能使 ATPG 實現高覆蓋率。ATPG 工具只需要得到測試圖形將重定向的指示,這樣未知值就可以通過IO賦值,同時恰當的數據被存出來,這些恰當的數據包括需要在IC頂層驗證的任何時鐘或被約束引腳。

圖2:利用分層測試方法,所有區塊的 ATPG 工作可以在各內核上獨立完成。

評論