基于DM6446 中的高清數字視頻顯示接口設計方案

本文通過直接對芯片內部PLL以及VENC時序發生器的配置,產生顯示高清數字視頻所需的像素時鐘和同步控制時序信號,VENC 的輸出再經由TFP410提供的DVI顯示接口,最終實現了720P,1080P以及WUXGA分辨率下的高清數字視頻顯示,最終說明了本文所提出方案是易用、可行,具有實用性。

0 引言

TI 公司推出的DM6446 芯片在視頻處理領域被廣泛的使用,其基于ARM+DSP 雙核架構,同時具備了通用處理器(GPP)和專用數字處理器(DSP)的功能。它的視頻處理子系統(VPSS)同時包含了視頻采集的接口-- 視頻處理前端(VPFE),以及視頻顯示的接口--視頻處理后端(VPBE),這也是其能夠在視頻處理領域嶄露頭角的重要組成部分。DM6446能夠同時支持標準時序PAL/NSTC制式的數字和模擬視頻輸出,也支持非標準模擬VGA顯示接口,但這模式的視頻輸出的分辨率都較低,不適用于需要大分辨率顯示的場合。

要讓其支持高清顯示,就必須通過編程配置,實現高清顯示所需的時序控制信號。DM6446 支持并行的24位RGB888視頻數據輸出,經過外部芯片編碼轉換后送給顯示器顯示。這里采用的編碼芯片是TFP410,它接收并行的圖像數據以及同步控制信號,經過編碼轉換后,按照DVI標準傳輸給顯示器進行顯示[5].

文中第1 部分介紹了高清數字視頻接口設計的整體結構;第2部分介紹了TFP410的配置和使用方法;第3部分介紹了實現高清數字顯示所需的VENC的參數配置方法,同時結合OSD 窗口配置給出了實際的高清數字視頻顯示結果。

在目標板上,720P(1 280×720@60 Hz)、1 080P(1 920×1 080@60 Hz)以及WUXGA(1 920×1 200@60 Hz)分辨率的數字視頻顯示都能夠穩定運行,說明這里提出的高清數字視頻顯示接口設計方案是正確、可行的,對基于DM6446高清數字視頻顯示應用具有實際意義。

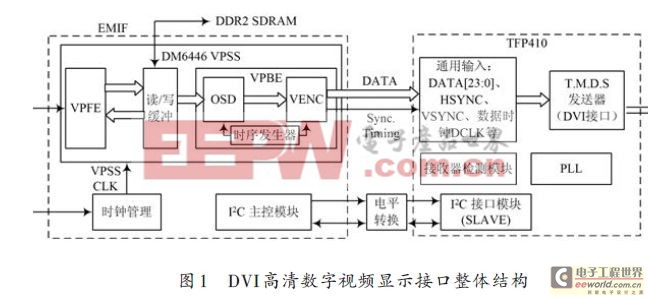

1 高清數字視頻顯示接口整體結構

整個DVI 高清數字視頻顯示接口的結構如圖1 所示,主要可分為DM6446 的VPSS 接口部分以及DVI 驅動器TFP410接口兩部分。

VPFE從外部采集到視頻數據后存儲于DDR2中的指定位置,VPBE 中的在屏顯示模塊(OSD)也在DDR2中有對應的緩沖區,這些模塊與DDR2之間的數據傳輸都有專門的讀寫邏輯控制,以保證數據的傳輸帶寬滿足系統要求。對于高清顯示的支持,主要是對VPBE中的視頻編碼模塊(VENC)的時序控制部分的正確配置,包括VENC時鐘、OSD時鐘和輸出給TFP410的像素時鐘,以及視頻的行同步、場同步信號等,這些在后面會有具體介紹。

TFP410 主要起到視頻數據編碼的作用,將前面由VENC 輸出的圖像數據以及同步控制信號經編碼后用差分串行的方式(T.M.D.S)傳輸給顯示器,這可以保證數據在傳輸過程中的抗干擾能力。同時,TFP410 包含有一個I2C 接口,使得DSP 可以通過它配置DVI驅動器的工作模式。在系統上電后,TFP410 能夠檢測到顯示器是否連接,這樣DSP便可以通過檢查相應的狀態位來決定是否發送視頻數據。

2 TFP410 的工作模式配置

TFP410 支持的最高像素時鐘為165 MHz,能夠滿足高清數字視頻顯示的需求,其總共有兩種配置方法:

引腳直接配置法和I2C配置法。采用引腳直接配置的方法,上電后芯片可以直接工作在既定模式下,但是功能比較單一,工作模式不夠靈活。采用I2C配置的方法,便可以根據需要調整芯片的工作模式,包括數據采集的時鐘沿、數據位寬、數據采集延時等。通過讀取TFP410中的相關狀態寄存器,DSP端的應用程序還能夠獲得圖像傳輸的相關信息,包括水平、垂直全局分辨率,以及顯示器是否連接等。

TFP410的I2C 可訪問寄存器共有256個,其中絕大多數是保留使用的,在實際使用中,需要操作的寄存器更是少數。在這里,只需配置寄存器CTL_1_MODE、CTL_2_MODE、CTL_3_MODE 即可,其他的都可以按照默認配置,一般情況下無需改變。設置CTL_1_MODE.

PD#=1 使芯片從節電模式恢復到普通模式;設置CTL_1_MODE.HEN=1、CCTL_1_MODE.VEN=1使能行、場同步信號輸入,設置CCTL_1_MODE.TDIS=0 使能芯片T.M.D.S 電路輸出。CTL_2_MODE主要用于主機檢測顯示器狀態,而CTL_3_MODE 則主要負責數據采集過程中的時延控制。對TFP410 的基本配置流程如圖2所示。

在圖2 中,僅僅是列出了必須配置的寄存器,其余寄存器可以不用修改,一般不影響使用。配置CTL_1_MODE=0×37,使器件工作模式為:24 位數據寬度、單端像素時鐘(VCLK)輸入、在VCLK 上升沿采樣輸入數據。配置好TFP410后,DM6446只要按照高清數字視頻的標準時序輸出相應的圖像數據和同步控制信息,就能夠將OSD 上的內容通過DVI 接口顯示到LCD 顯示器上。

評論