一種基于FPGA的多通道高速采樣系統設計

本文引用地址:http://www.104case.com/article/236795.htm

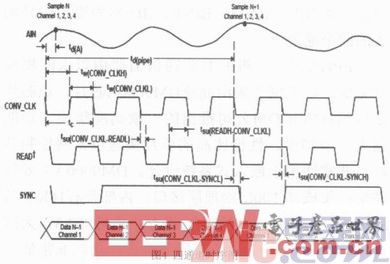

在轉換過程中ADC有一個自由運行的外部輸入時鐘CONV CLK。隨著每一個CONV CLK信號下降沿,四個通道模擬信號轉換后的值提供給相應的讀出信號中的數據總線。READ+是,CS1三者的邏輯集成信號,READ+為低電平時表示讀有效。信號SYNC是低電平時,第一個通道的數據到數據總線,隨后SYNC拉高,第二、三、四通道的數據按順序依次讀取。

3.2 多片AD的同步采樣及并行處理

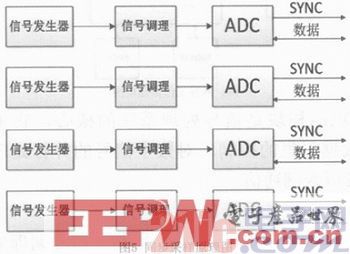

單個AD的控制完成后,就很容易擴展到對四片AD的控制。在采集多通道數據時,需要保持同步采樣,本設計采用的方法是每一路信號通過各自的信號調理電路和ADC轉換結束后,ADC保持數據,由FPGA依次讀取。

在硬件布局時,四片AD共用數據線,讀寫信號和AD轉換時鐘信號。因此FPGA通過寫命令同時啟動這四片AD芯片,十六個通道的模擬信號進入AD。每片AD都有一個數據同步信號SYNC,當判斷得到四片AD中的某個SYNC信號是低電平時,則可認為十六道數字信號已同步到位,通過片選信號的切換依次讀取各個AD芯片的數據并暫時儲存在寄存器中。也可以根據自己需求,開啟和關閉某些AD,選擇特定的通道數據進行讀取。同步采樣原理圖如圖5所示。

3.3 自定義指令

自定義指令是FPGA的嵌入式軟核nios ii的一大特色,nios ii有著一個開放式的ALU,用戶可以根據自己的要求添加自定義指令來實現應用需求,大大體現了nios ii軟核的靈活性。自定義指令的功能是運用Verilog語言,由電路模塊來完成的。因此,相比較利用C語言編程來實現功能,自定義指令具有執行速度快的顯著特點。Nios ii支持四類自定義指令:組合邏輯指令、多周期用戶自定義指令、擴展用戶自定義指令、內部寄存器自定義指令來滿足各種應用情況。

本設計中旋轉機械的振動信號雖然在硬件中經過了信號調理,但是由于元器件間參數的問題,仍舊會存在數據的偏差,運用了自定義指令中的多周期用戶自定義指令將數據進行修正。多周期指令需要數據指令和邏輯指令。利用start信號開始執行指令,done信號來表示執行結束,可以返回結果。

同時對于采集得到的數據進行傅里葉變換、濾波等處理,通過自定義指令也能實現,提升了FPGA的信號處理能力。

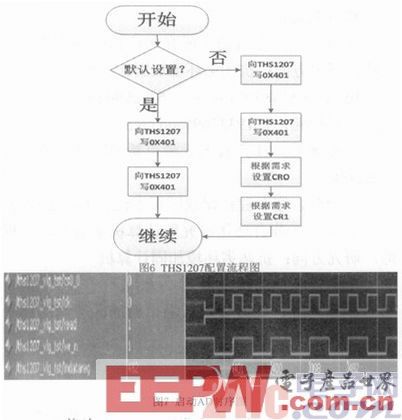

4 AD時序仿真

仿真在FPGA的開發中扮演了重要的角色,利用modelsim仿真軟件來對編好的AD程序進行時序驗證。AD正式工作前,需要通過向AD內部控制寄存器、CR1寫命令啟動AD,然后才能讀取數據。啟動AD芯片THS1207的流程圖如圖6所示,啟動AD的仿真結果如圖7所示。

AD芯片THS1207正常啟動后就可以開始讀取各個通道的數據,由于本設計是十六個通道依次采樣,采樣結束后,需要通過片選控制信號依次讀取各個通道的數據,仿真結果如圖8所示。

從仿真結果驗證得到編寫的AD程序可以完成十六道采樣的設計要求。

5 實驗結果

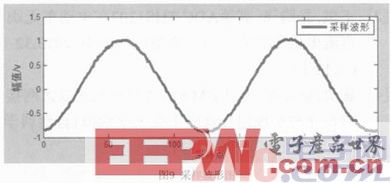

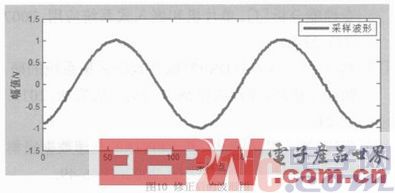

實驗采用AD四通道同步采樣,利用信號發生器產生正弦波,選擇同步采樣方式對每個正弦波采樣128點,通過以太網傳送到上位機,采樣得到的波形如圖9所示。

可以利用FPGA的自定義指令,根據需求將得到的數據進行處理,如圖10,對得到的波形數據進行偏置為-10和放大倍數為1.05的修正。

實驗中當信號發生器發出正弦波的頻率達到3000Hz時,即采樣頻率達到384kHz時,FPGA采集波形能力達到了最大值,相當于180000r /min的旋轉機械的基頻信號。當超過3000Hz時,采樣得到的波形會出現毛刺現象。分析原因,主要是由于nios ii進、出中斷服務程序,以及中斷服務程序中對采樣數據的讀取需要花費一定的時間。

6 結束語

本設計利用FPGA并行技術、自定義模塊化設計以及nios ii的特色功能即自定制指令,實現了對于旋轉機械振動信號的多通道高速同步采樣。顯示了FPGA可編程、設計靈活、高速的特點,同時也驗證了基于FPGA的多通道高速采樣系統的可行性。

根據實驗結果和理論的最大采樣速度還有差距,可以進一步改進系統設計,例如采用DMA優化程序,提高速率。

評論