一種基于FPGA的視頻圖像畫面分割器設(shè)計

摘要:為了解決在一個屏幕上收看多個信號源的問題,對基于FPGA技術(shù)的視頻圖像畫面分割器進行了研究。研究的主要特色在于構(gòu)建了以FPGA為核心器件的視頻畫面分割的硬件平臺,首先,將DVI視頻信號,經(jīng)視頻解碼芯片轉(zhuǎn)換為數(shù)字視頻圖像信號后送入異步FIFO緩沖。然后,根據(jù)畫面分割需要進行視頻圖像數(shù)據(jù)抽取,并將抽取的視頻圖像數(shù)據(jù)按照一定的規(guī)則存儲到圖像存儲器。最后,按照數(shù)字視頻圖像的數(shù)據(jù)格式,將四路視頻圖像合成一路編碼輸出,實現(xiàn)了四路視頻圖像分割的功能,提高了系統(tǒng)集成度,并可根據(jù)系統(tǒng)需要修改設(shè)計和進一步擴展功能,增加了系統(tǒng)的靈活性,適用于多種不同領(lǐng)域。

本文引用地址:http://www.104case.com/article/236794.htm隨著計算機、DSP、超大規(guī)模集成電路等技術(shù)的發(fā)展,畫面分割器開始采用硬件設(shè)計。首先,將各路視頻信號轉(zhuǎn)換成數(shù)字視頻信號;然后,在數(shù)字領(lǐng)域?qū)Ω髀芬曨l信號進行處理。使電路的設(shè)計、調(diào)試得到了很大的改善。但是,設(shè)計中所使用的獨立的邏輯電路較多,有的甚至使用專用的DSP芯片去處理視頻畫面的分割。雖然可以滿足對視頻圖像數(shù)據(jù)處理速度的要求,但是還需要外加CPU去協(xié)調(diào)系統(tǒng)工作,使得整個系統(tǒng)仍顯得體積較大,而且系統(tǒng)成本較高。隨著半導體加工工藝的不斷發(fā)展,F(xiàn)PGA在結(jié)構(gòu)、速度、工藝、集成度和性能方面都取得了很大的進步和提高。本文將詳細介紹基于FPGA開發(fā)技術(shù)的視頻圖像畫面分割器的軟硬件設(shè)計與實現(xiàn)。

1 系統(tǒng)總體設(shè)計

本系統(tǒng)選用Altera公司的CycloneIII系列中的EP3C40F780C7型號FPGA作為核心處理芯片,提出和設(shè)計了一個多路視頻圖像數(shù)據(jù)的采集、處理、顯示,實現(xiàn)視頻圖像畫面分割器。

Cyclone III系列FPGA是Altera公司的低功耗、高性能和低成本的可編程邏輯器件,具有獨特的低功耗體系結(jié)構(gòu),以非常低的成本提供豐富的存儲器和專用乘法器資源。在視頻和圖像處理等高強度算法應(yīng)用中,這些特性使該FPGA成為ASSP、ASIC以及分立數(shù)字信號處理器的理想替代方案。

1.1 硬件結(jié)構(gòu)設(shè)計

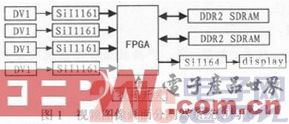

整個系統(tǒng)主要由DVI接口電路、DVI信號解碼電路、FPGA及其配置電路、DDR2 SDRAM數(shù)據(jù)存儲電路及DVI信號編碼電路組成,系統(tǒng)結(jié)構(gòu)框圖如圖1所示。

從圖1中可以看出,從DVI接口接收到DVI信號后通過解碼芯片SiI1161進行解碼,轉(zhuǎn)換成并行的數(shù)字信號,然后進入FPGA對四路視頻信號進行提取、存儲、合成等功能,進行處理后的數(shù)據(jù)通過編碼芯片SiI164再轉(zhuǎn)換為DVI視頻信號,就可以接到顯示器上顯示了。

1.2 軟件結(jié)構(gòu)設(shè)計

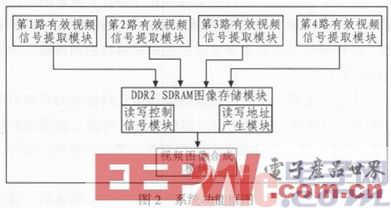

系統(tǒng)的軟件設(shè)計是系統(tǒng)功能實現(xiàn)的關(guān)鍵。在系統(tǒng)的硬件平臺的基礎(chǔ)上,通過對FPGA編程實現(xiàn)對視頻解碼芯片輸出的實時數(shù)字視頻數(shù)據(jù)接收,并根據(jù)畫面合成需要,對有效視頻圖像數(shù)據(jù)進行提取和存儲,然后將各路視頻數(shù)據(jù)合成一路輸出到顯示器。系統(tǒng)實現(xiàn)功能的系統(tǒng)框圖如圖2所示。

以下重點介紹一下視頻信號的提取和合成。

1.2.1 提取模塊設(shè)計

1)圖像提取原理

視頻畫面盡管看起來好像是連續(xù)運動的,其實那是一系列靜止的圖像,這些圖像切換得足夠快,使得畫面看起來像是連續(xù)運動的,如圖3所示。一種稱為場同步(vertical sync)的特定時序信息被用于指定新圖像從什么時候開始顯示;每張靜止圖像是由掃描線(scan line)組成的,即沿著顯示器從上到下、一行接著一行進行顯示的數(shù)據(jù)線,另一種稱為行同步(horizontal sync)的時序信息用于指定新掃描線什么時候開始顯示。

行同步和場同步信息通常通過以下3種方式之一進行傳輸:

①單獨的行同步和場同步信號;

②單獨的復(fù)合同步信號;

③嵌入視頻信號的復(fù)合同步信號。

本系統(tǒng)采用的是數(shù)字視頻,采用的是技術(shù)①。

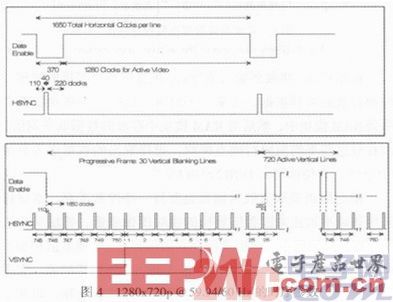

DV支持超過1 600×1 200的PC圖形分辨率和包括720p、1 080 i和1 080 p的HDTV分辨率,本設(shè)計采用的輸入分辨率為1 280×720/60 Hz,像素時鐘為74.25 MHz。DVI信號經(jīng)SiI1161解碼后得到帶像素時鐘的24位并行R、G、B數(shù)字信號及H、V、DE信號,它們之間的相互關(guān)系如圖4所示。

其中,當DE為1時,處理有效視頻,當DE為0時,處理HSYNC和VSYNC信號。SiI1161輸出的數(shù)字視頻信號一幀由750行視頻數(shù)據(jù)組成,每一場有效視頻行為720行,每一行又有1 650個像素,其中有效像素有1 280個,這些是在視頻圖像合成過程中要用到的數(shù)據(jù),每一個像素都包含R、G、B 3種信號。

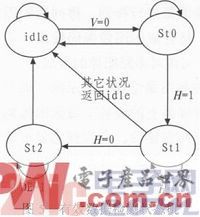

本設(shè)計根據(jù)H、V、DE信號對有效視頻數(shù)據(jù)進行定位,并根據(jù)圖像合成的需要把所需的有效視頻數(shù)據(jù)提取出來。在實現(xiàn)的過程中利用狀態(tài)機來判斷有效視頻數(shù)據(jù),如圖5所示。

狀態(tài)機缺省狀態(tài)為idle狀態(tài)。先在idle狀態(tài)檢測場信號由高變低,進入有效數(shù)據(jù)行,再判斷H與DE的高低狀態(tài),進而檢測到有效視頻數(shù)據(jù),當H由高變低,DE為高的這段視頻數(shù)據(jù)則為有效視頻數(shù)據(jù)。這樣則可以根據(jù)視頻圖像合成的需要對視頻數(shù)據(jù)進行選擇提取。

2)圖像提取模塊設(shè)計

基于上述有效視頻數(shù)據(jù)的提取原理可以提取任何一個數(shù)據(jù)行或任何一個象素,由于不同的圖像合成需要提取的有效視頻數(shù)是不同的。本設(shè)計為四畫面分割,需要對每一路輸入信號進行1/4壓縮,即需要對有效數(shù)據(jù)進行隔行隔點提取。有效視頻數(shù)據(jù)提取程序框圖如圖6所示。

fpga相關(guān)文章:fpga是什么

評論