EMI/EMC設計講座(二)磁通量最小化的概念

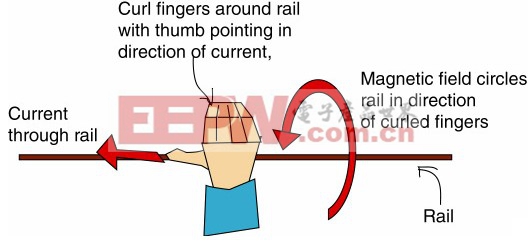

根據Maxwell方程式,移動走線中的電荷可以產生一電流,此電流又會產生一磁場,這種被移動電荷產生的磁場稱作「磁通線(magnetic lines of flux)」。使用「右手法則(Right-Hand Rule)」可以輕易地指出磁通線的方向,如附圖三所示。右手拇指代表走線電流流動的方向,其余卷曲的手指包圍著走線,代表磁場或磁通線的方向。此外,時變磁場會產生一個垂直的電場。射頻輻射是此磁場和電場的組合。藉由輻射或導電的方式,磁場和電場會離開PCB結構。

請注意,此磁場是環繞著一個封閉式回路的邊界運行。在PCB中,來源驅動端產生射頻電流,并經過走線將射頻電流傳送到負載。射頻電流必須經過一個回傳系統回到來源端(Ampere定律)。其結果是,產生了一個射頻電流回路。這個回路不必然是環狀的,但通常是呈回旋狀。因為這個過程會在回傳系統內產生一個封閉回路,因此會產生一個磁場。這個磁場又會產生一個輻射的電場。在近場處,是由磁場成份主導;然而在遠場處,電場對磁場的比率(波阻抗)大約是120πΩ或377Ω,和來源端無關。所以明顯可知,在遠場處,磁場可以使用一個循環型天線和一個相當靈敏的接收機來測量。接收準位將是E/120π(A/m,若E的單位是V/m)。同理,可以應用到電場,能在近場處使用合適的測量儀器來測量電場。

圖三:右手法則

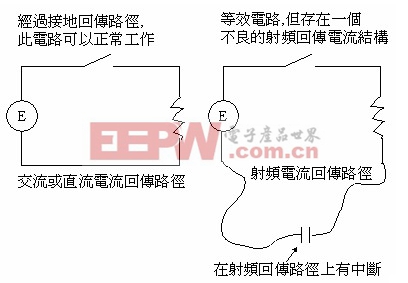

射頻如何存在于PCB中的另一種簡單解釋,可由附圖四和五中得知。在這里以時域和頻域來分析典型的電路。根據Kirchhoff和Ampere定律,如果要使電路能夠工作的話,一個封閉型回路電路必須存在。Kirchhoff電壓定律表示:在一個電路中,環繞任何一個封閉路徑的電壓總合必須是零。Ampere定律表示:給定 的電流會在一個點上產生磁感應,它是以電流單元和電流與那個點的相對位置來計算的。

若封閉回路型電路不存在,訊號是無法透過傳輸線,從來源端到達負載的。當開關關閉時,電路就成立,交流或直流電流就開始流動。在頻域,我們將此電流視為射頻能量。其實,并沒有存在兩種不同的電流(時域或頻域電流)。始終只有一種電流存在,它可以在時域或頻域中呈現。從負載到來源端的射頻回傳路徑也必須存在,否則電路將無法工作。因此,PCB結構必須遵守Maxwell方程式、Kirchhoff電壓定律,和Ampere定律。

Maxwell方程式、Kirchhoff和Ampere定律全部都在說:若要使一個電路正常工作或依期望的目的工作,一個封閉回路型網絡必須要存在。附圖四表示了這樣的典型電路。當一條走線從來源端到達負載,一個回傳電流路徑也必須要存在,這是Kirchhoff和Ampere定律所規定的。

圖四:封閉回路型電路

圖五:一個封閉回路型電路的描述

如附圖五所示,一個開關和來源驅動端(E)串聯。當開關關閉時,電路按照期望結果正常工作;當開關開啟時,則不具任何功能。對時域而言,期望

訊號從來源端到達負載。此訊號必須具有一個回傳路徑,才能使此電路成立,這通常是經過一個0V(接地)的回傳結構(Kirchhoff定律)。射頻電流的流動是從來源端到達負載,而且必須經過阻抗盡可能最小的路徑返回,通常它是經過一個接地走線或接地平面(鏡射平面)。射頻電流的存在,最好使用Ampere定律來說明。

磁通量最小化

在探討「EMI是如何在PCB內產生」之前,必須先明白「磁通線是如何在傳輸線中產生」的基本機制,因為后者是前者的一個基本概念。磁通線是一電流流經一個固定或變動的阻抗所產生的。在一個網絡中的阻抗,永遠都存在于走線、組件的焊線、通孔(via)……等。如果磁通線有存在于PCB內,根據Maaxwell方程式,射頻能量的各種傳送路徑也一定存在。這些傳送途徑可能是經過自由空間輻射出去,或經過纜線的相互連接傳導出去。

為了消除PCB內的射頻電流,必須先介紹「磁通量消除(flux cancellation)」或「磁通量最小化(flux minimization)」的概念。因為磁通線在傳輸線中,以逆時鐘方向運行,如果我們使射頻回傳路徑,平行且鄰近于來源端的走線,在回傳路徑(逆時鐘方向的場)上的磁通線,與來源端的路徑(順時鐘方向的場)做比較,它們的方向是相反的。當我們將順時鐘方向的場和逆時鐘方向的場相互組合時,可以產生消除的效果。如果在來源端和回傳路徑之間,不需要的磁通線能夠被消除或減至最少,則輻射或傳導的射頻電流就不會存在,除非是在走線的極小邊界上。消除磁通量的概念很簡單,但是在進行消除或最小化設計時,必須注意一些陷阱和容易疏忽的地方。因為一個小失誤,可能會引起許多額外的錯誤,造成EMC工程師更多偵錯和除錯的負擔。最簡單的磁通量消除法,是使用「鏡射平面(image plane)」。不管PCB布線是設計的多么好,磁場和電場都永遠存在。但是,如果我們消除了磁通線,則EMI就不存在。就是那么簡單!

在設計PCB布線時,要如何消除磁通線呢?目前有許多技巧可供參考,但是它們不是全部都和消除磁通線有直接關系,簡述其中的一些技巧如下:

●多層板具有正確的多層設置(stackup assignment)和阻抗控制。

●將頻率走線(clock trace)繞到回傳路徑接地平面(多層PCB)、接地網格(ground grid)的附近,單側和雙側板可以使用接地走線,或安全走線(guard trace)。

●將組件的塑料封裝內部所產生的磁通線,捕捉到0V的參考系統中,以降低組件的輻射量。

●警慎選擇邏輯組件,盡量減少組件和走線所輻射的射頻頻譜分布量。可以使用訊號緣變化率(edge rate)比較慢的裝置。

●藉由降低射頻驅動電壓(來自頻率產生電路,例如:TTL/CMOS),來降低走在線的射頻電流。

●降低接地噪聲電壓,此電壓存在于供電和接地平面結構中。

●當必須推動最大電容負載,而所有裝置的腳位同時切換時,組件的去耦合(decoupling)電路必須充足。

●必須將頻率和訊號走線做妥善的終結,以避免發生阻尼振蕩(ringing)、電壓過高(overshoot)、電壓過低(undershoot)。

●在選定的網絡上,使用數據線路濾波器和共模扼流圈(common-mode choke)。

●當有提供外部I/O纜線時,必須正確地使用旁路(非去耦合)電容。

●為會輻射大量的共模式射頻能量(由組件內部產生)之組件,提供一個接地的散熱器(heatsink)。

檢視上面所列的項目,可以知道, 磁通線只是「在PCB內會產生EMI」的部份原因而已。其它原因還有:

●在電路和I/O纜線之間,有共模和差模(differential mode)電流存在。

●接地回路會產生一個磁場結構。

●組件會輻射。

●阻抗不匹配。

請注意,大多數的EMI輻射是由共模準位產生的。在電路板或電路中,

這些共模準位可能會被轉變成最小的場。

結語

要消除PCB中的EMI,必須先從消除磁通量開始。但是,這是「說比做容易」,因為射頻能量是看不見、聞不著的。不過,藉由尋找射頻電流的位置與流動方向,并采用本文所介紹的幾項技巧,以及參照Maxwell方程式、Kirchhoff和Ampere定律,就可以逐漸縮小可疑的區域,找出正確的EMI位置,并消除它。

評論