TPS54350在信號處理系統中的應用(圖)

dc/dc轉換器tps54350可在信號處理系統中提供多個電壓,具有靈活、高效、緊湊等特點。

tps54350是具有內部mosfet的高效dc/dc轉換器,連續輸出電流為3a時,支持輸入電壓范圍為4.5~20v,可使設計人員直接通過中壓總線(而非依賴額外的低電壓總線)為dsp、fpga和微處理器供電。

特性和功能

tps54350的輸入電壓為4.5~20v,輸出電壓可調低至0.891v,pwm頻率固定為250khz、500khz或250~700khz的可調節范圍,還具有完善的保護功能。

tps54350的管腳功能如下。

● vin:電壓輸入引腳,必須旁路接一個低差錯秒比率(esr)為10μf的陶瓷電容;

● uvlo :低電壓鎖定輸出;

● pwrgd:開溝道輸出。引腳為低時,表示輸出低于期望的輸出電壓值。pwrgd比較器的輸出端有一個內部的上升沿濾波器;

● rt:頻率設置引腳。在rt引腳與地(agnd)之間接一個電阻器來設置轉換頻率。將rt引腳與地連或是懸空,可以來得到一個內部的備選頻率;

● sync:雙向io同步引腳。當rt引腳懸空或置低時,sync為輸出;當它與一個下降沿信號連接時,亦可作為一個輸入端口來同步系統時鐘;

● ena:使能引腳。低于0.5v時,芯片停止工作;懸空時被使能;

● comp:誤差放大器輸出;

● vsense:誤差放大器轉換節點,基準電壓值;

● agnd:模擬地,內部與感應模擬地電路連接。與pgnd和powerpad連接;

● pgnd:電源地,與agnd和powerpad連接;

● vbias:內部8.0v偏置電壓。引腳要接一個0.1μf的陶瓷電容;

● ph:相位,與外部l-c濾波器連接;

● boot:在boot引腳與ph引腳之間連接一個0.1μf的陶瓷電容。

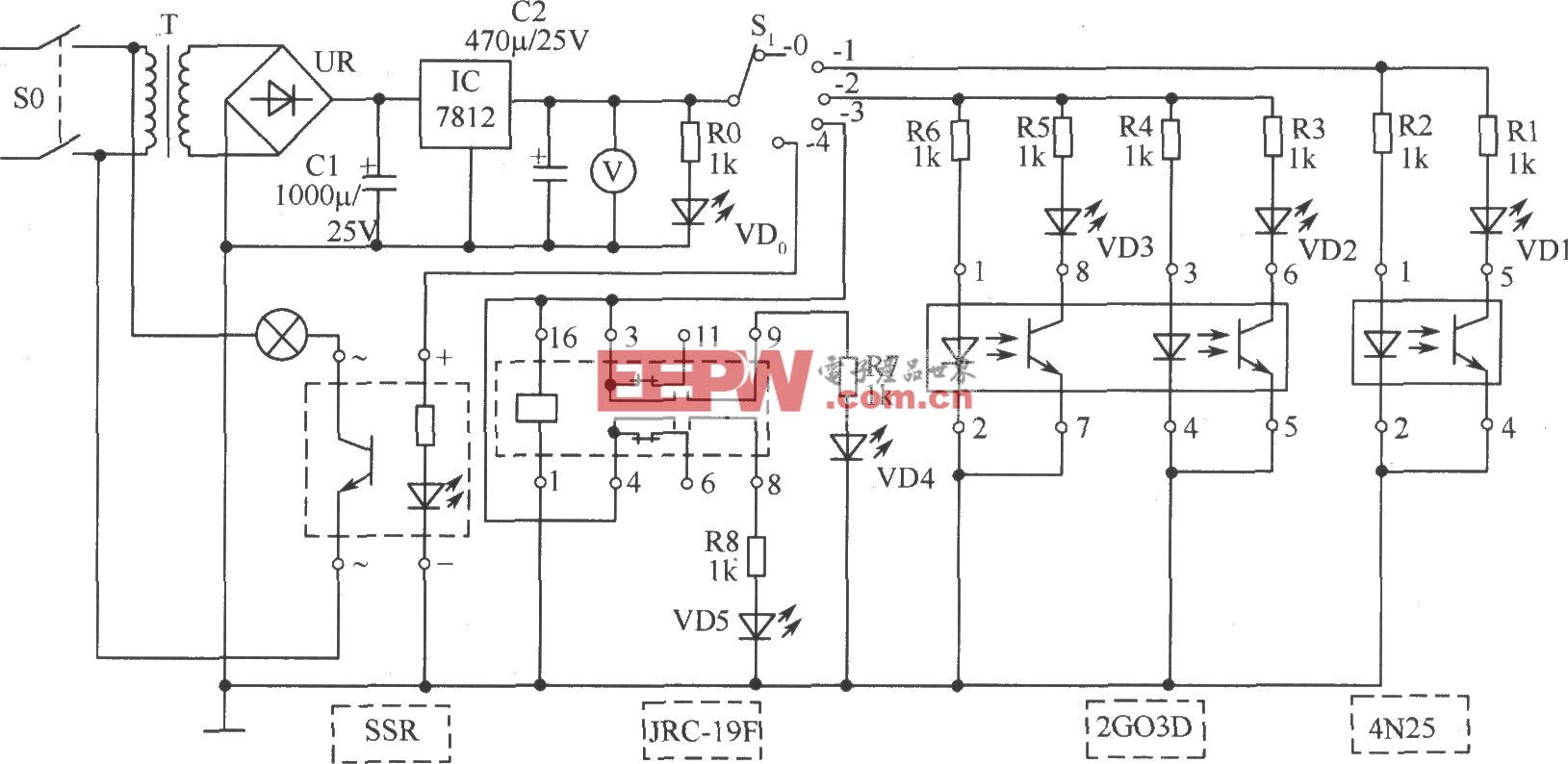

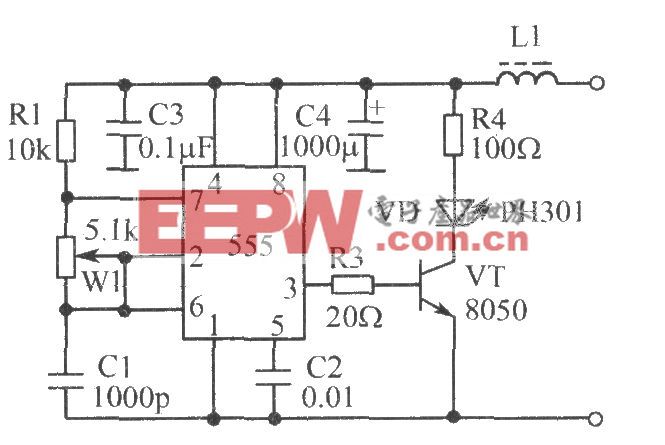

圖1是tps54350的實際應用電路圖,圖中給出的是其中的一種情況,其輸出電壓是可變的,通過改變電阻r2的值,來得到期望的輸出電壓值。圖中的輸入電壓為12v,輸出電壓為3.3v,其中r2的計算公式為 r2 = r1 x 0.891/(vo - 0.891),此時的r2阻值為374ω,r1=1kω。

表1中給出當r1=1kω和r1=10kω時的幾種輸出電壓之下的r2的值。本文所設計的系統中,就是運用圖1所示的電路來實現的。根據不同的輸出電壓要求,賦給r2不同的阻值,其阻值的取法可參照表1。另外,對于一個設計者來說,在設計電路時要考慮到以下幾個因素,見表2。本系統中的r1阻值為1kω。

在信號處理系統中的應用

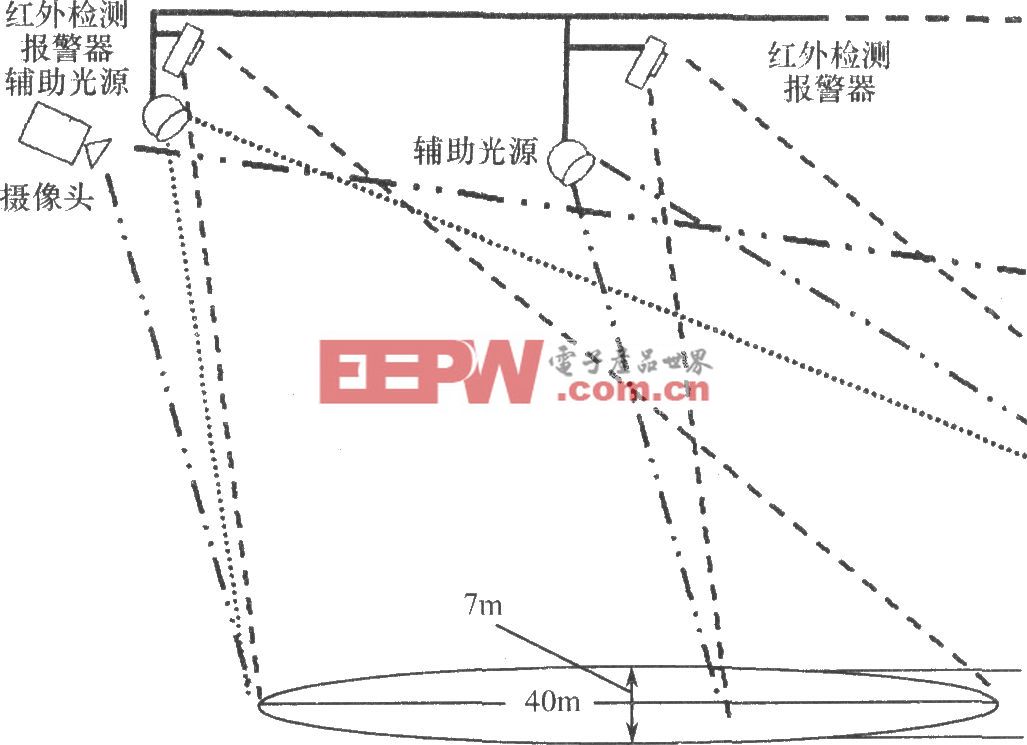

本信號處理系統采用的是adi公司的adsp ts101s芯片所組成的多片某仿真雷達信號處理系統,系統主要由五片dsp、一片cpld和七片tps54350組成。在以往使用max1951的經驗基礎上,經過多方面的設計考慮,系統采用了tps54350芯片。從表1可以看出,tps54350可以輸出3.3v和1.2v的電壓。系統中的dsp采用的是240mhz的時鐘,每個指令周期約為4.17ns。根據adsp ts101s的操作條件可知,當溫度為25℃,時鐘cclk為250mhz時,典型情況下的vdd(1.25v)供電電流的典型值為1.2a,vdd_io的供電電流小于137ma。tps54350的額定輸出電壓為3a,所以此系統的設計是合理的。

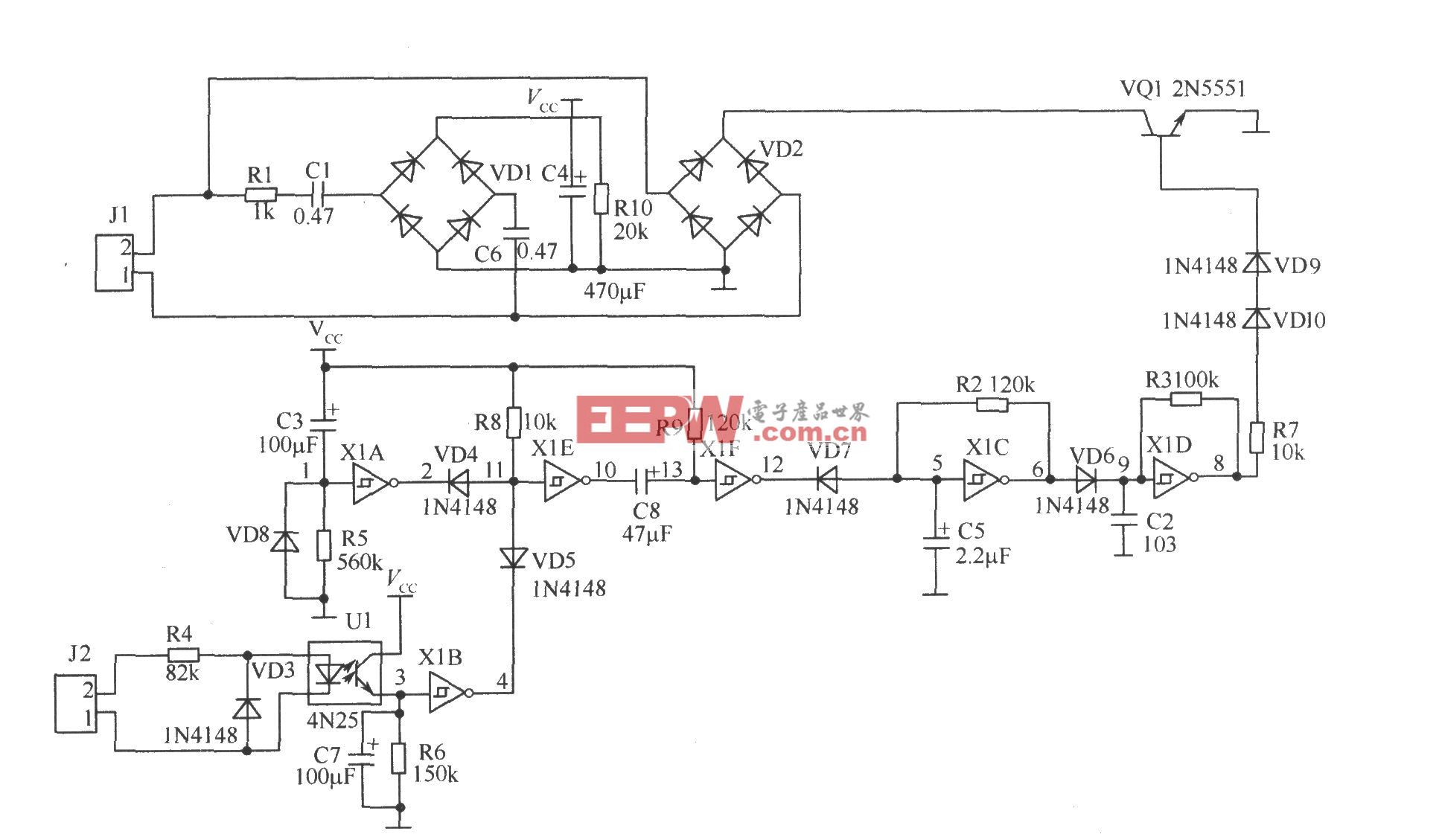

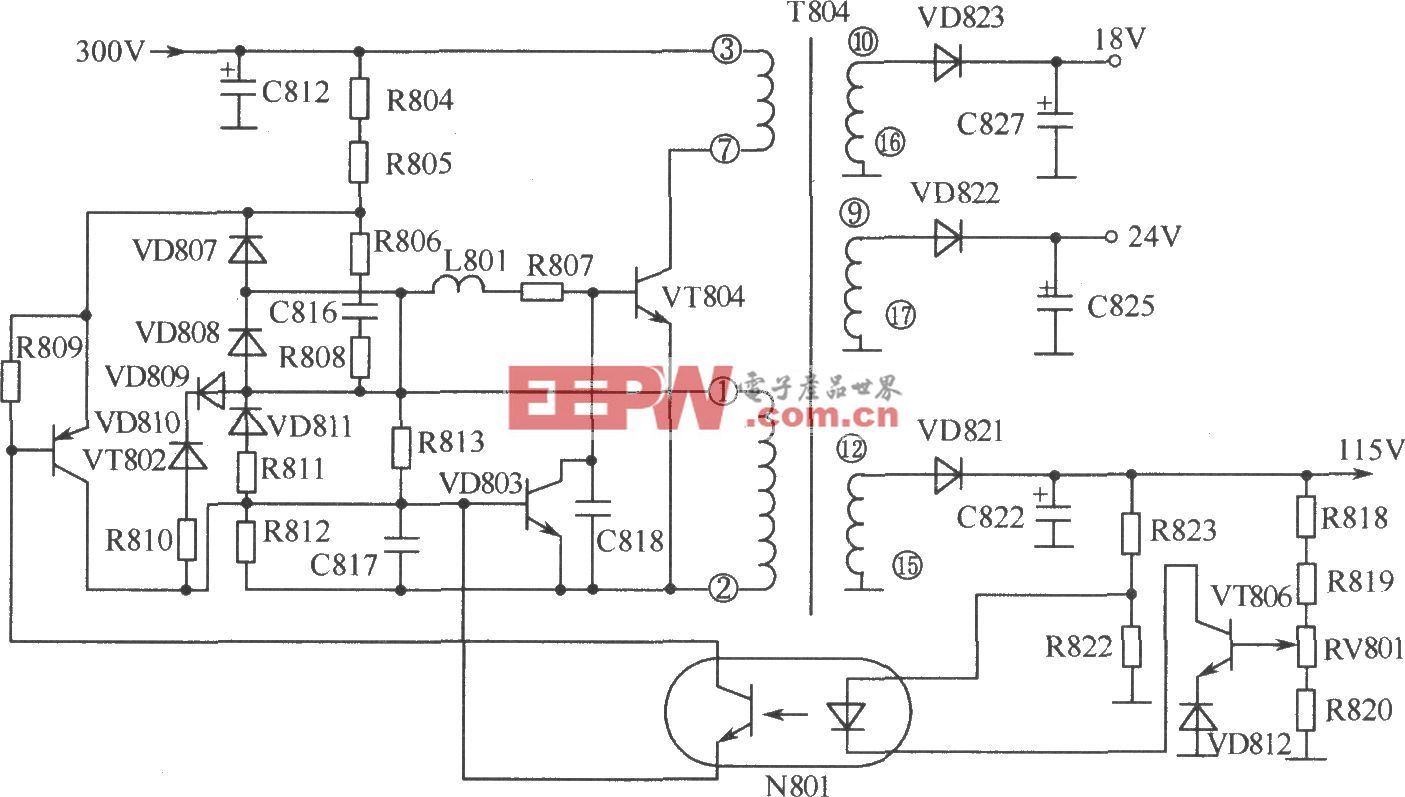

tigersharc dsp有三個電源,其中數字3.3v(vdd_io)為i/o供電;數字1.2v(vdd)為dsp內核供電;模擬1.2v(v)為內部鎖相環和倍頻電路供電。系統將主機送來的5v經過tps54350得到3.3v和1.2v的電壓。各片dsp的數字1.2v(vdd_a)電源各由一片tps54350供給。五片dsp內部模塊1.2v(vdd_a)由同一dsp芯片的vdd(+1.2v)經濾波網絡后解決。五片dsp的i/o 3.3v電源直接由主機送來的5v經過tps54350得到的3.3v統一供給,同時也提供cpld(ep1k30)的vcc_io(+3.3v)的電壓。其中cpld的vcc_int(+2.5v)利用tps54350輸出的+2.5v的電壓來供電。本文給出了系統的供電框圖,如圖2所示。圖3中給出了單片dsp的內核供電框圖及外圍電路配置。

tps54350采用的是小型16引腳htssop封裝。根據以往的經驗,建議設計者在設計pcb時,最好給trs54350加上散熱片,電源線盡量粗。在tps54350的前后均加上了濾波網絡,盡量保證得到比較合適的電壓。

系統中的ep1k30產生上電復位波形和時序控制。由于ep1k30需要一個配置芯片,而且它和dsp存在一個上電先后的問題。也就是說,在上電后,如果cpld芯片完成配置文件的讀入時,dsp仍未上電穩定,則應充分延長tstart_io的低電平時間,以避免dsp上電未穩定而cpld上電波形已結束。因此,應保證dsp上電穩定先于cpld芯片配置文件的讀入,此問題在系統設計時應予以充分重視,否則dsp將無法正常工作。tigersharc dsp要求數字3.3v和1.2v應同時上電。若無法嚴格同步,則應保證內核電源1.2v先上電,i/o電源3.3v后上電。本系統在數字3.3v輸入端并聯了一個大電容,而在數字1.2v輸入端并聯了一個小電容,其目的就是為了保證3.3v充電時間大于1.2v充電時間,以便很好地解決電源供電先后的問題。

參考文獻

1 4.5v to 20v input,3a output synchronous

pwm switcher with integrated fet

(swift), october 2003-revised october

2004,texas instruments inc

2 adsp-ts101s tigersharc embedded processor

prelimianry datasheet.rev.pra,june 2000,

analog devices,inc

3 劉書明,蘇濤,羅軍輝. tigersharc dsp

應用系統設計.電子工業出版社,2004.5

評論