整個時序程序信號總流程圖如圖4所示。程序總共由7個模塊組成:輸入同步時鐘模塊產生頻率20 MHz的主時鐘CLK,CLK 通過分頻模塊產生頻率36 kHz 的CLK1 和頻率5 MHz 的CLK2;信號控制模塊在主時鐘CLK 的同步作用下分別產生控制信號VClr、VSHClr 和HClr;輸入處理模塊對輸入主時鐘CLK做去抖動處理后輸出時鐘信號CLK0;V 信號產生模塊輸出光積分區域行轉移所需的12 kHz 占空比為50%的三相時鐘信號V1、V2、V3;VHS信號產生模塊輸出12 kHz占空比小于5%的移位時鐘信號VHS1、VHS2、VHS3;H信號產生模塊輸出水平移位讀出區域所需的20 MHz占空比50%的四相時鐘信號H1、H2、H3、H4,以及FOG讀出時鐘信號和RG復位脈沖信號。本文引用地址:http://www.104case.com/article/228012.htm

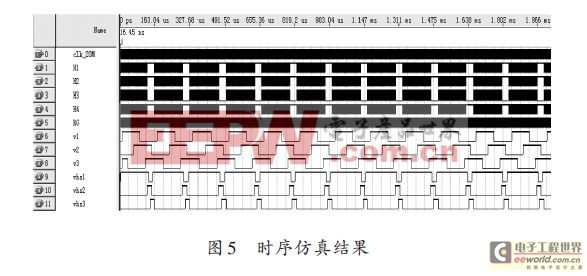

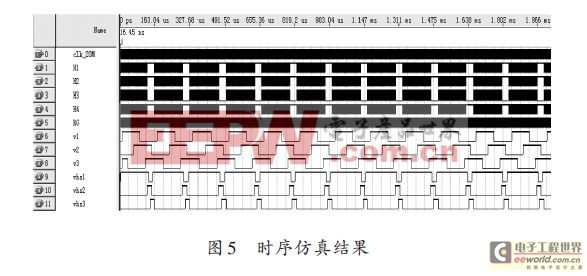

3.2 時序仿真結果

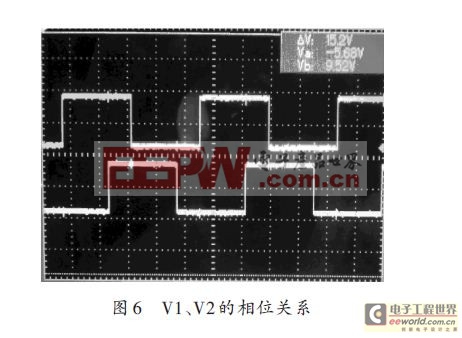

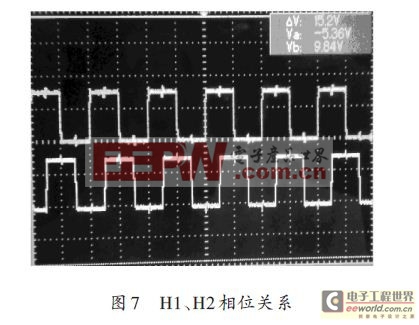

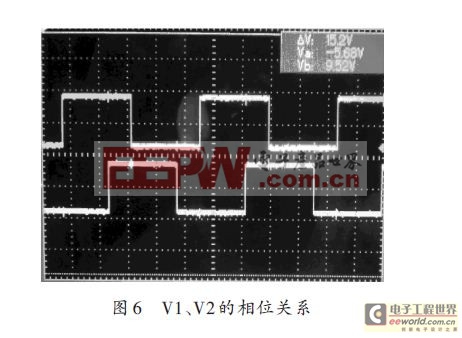

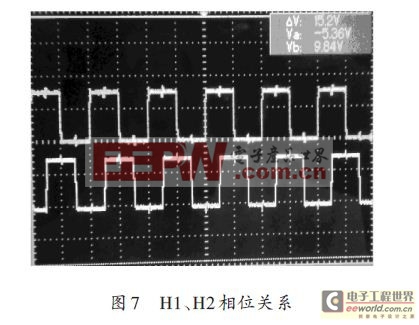

時序設計采用Altera公司的Quartus Ⅱ作為開發平臺,EP3C25Q240為硬件平臺。總的時序仿真結果如圖5所示,結果表明所有仿真信號滿足2.2節中的信號要求;圖6為FPGA上測得V1、V2的相位關系,圖7為FPGA上測得H1、H2相位關系,結果表明相位關系正確,能夠保證每個時刻至少有一個高電平和一個低電平,保證像元電荷的正常讀出。

4 結語

時序在硬件電路中成功驅動了TDICCD8091工作,驗證了軟硬件的正確性和準確性。程序設計利用同步時鐘控制全局電路的思想,避免競爭與冒險,提高了程序的可靠性;采用模塊化設計思想提高程序的可重用性、可測試性、可讀性及可維護性;狀態機的設計方法提高了程序運行的穩定性。

評論