基于FPGA的TDICCD8091 驅動時序電路設計

0 引言

本文引用地址:http://www.104case.com/article/228012.htm時間延時積分電荷耦合器件(Time Delay and Integra-tion Charge Coupled Devices,TDICCD)易于實現實時成像,可與小相對孔徑的光學系統配合成像,從而大幅度減少遙感相機的體積和質量,因此廣泛應用在航空航天、火控系統和遠海探測等領域。現場可編程邏輯門陣列(FPGA)在航空航天、工業自動化、儀表儀器、計算機設計與應用、通信、國防等領域的電子系統中的技術含量正以驚人的速度提升。完整的電子系統在單一FPGA芯片中實現早已成為現實,電子類新技術項目的開發也更多地依賴于FPGA技術的應用。

TDICCD是一種時間延遲積分圖像傳感器件,精準可靠的時序邏輯信號是TDICCD工作的最基本條件,是保障整個系統有效工作的關鍵,闡述了以FPGA為開發平臺設計TDICCD8091驅動時序的全過程。

1 TDICCD的特點及工作原理

1.1 TDICCD的特點

TDICCD 是一種具有面陣結構,線陣輸出的CCD,它的列數是一行的像元數,它的行數是TDICCD的級數N,較普通的線陣CCD 而言,它具有多重級數延時積分的功能。TDICCD 器件利用物體的運動速度與行轉移速度同步方式,對物體進行多次(N級)曝光,并對其信號進行累加,隨著TDI級數增加,信號隨TDI級數(N) 成線性增加,而噪聲隨TDI級數成平方根增加,TDICCD的信噪比(SNR)增加N 倍,從而獲得高的靈敏度和信噪比。利用曝光時間與使用的TDI級數成比例的關系,在不改變幀頻的情況下,通過選擇TDI級數,改變器件的曝光次數,使器件實現在不同照度下對目標正常成像。

1.2 TDICCD的工作原理

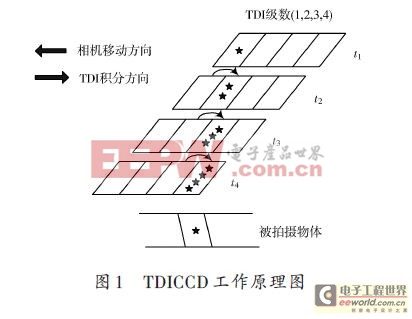

TDICCD相機工作原理如圖1所示。相機攝像時隨衛星向前移動,對地面同一靜止目標物體多次曝光成像,被拍攝物體為地面上靜止的星星。在t1 時刻,星星在第1級(行)TDICCD上曝光成像,產生電荷信號;t2 時刻,由于相機向前運動,經過了一個行周期后,第2 級TDICCD 再次對同一個星星曝光成像,產生電荷信號。

與此同時,時鐘信號驅動第1級TDICCD 上產生的電荷轉移到第2 級TDICCD 上。這樣,該行TDICCD 不僅包括此次曝光產生的電荷,而且也包括前一級轉移來的電荷,使電荷量增加了1 倍。依此類推,若TDICCD 的級數為N,相機輸出信號將增加為原來的N 倍。圖1中設定TDI 的級數為4 級,因此在t4 時刻,在TDI 的第4 級(行)星星曝光產生的電荷量為原來的4倍。

2 設計目標分析

2.1 TDICCD8091簡介

TDICCD8091是美國仙童公司的一款9 216×128的高速光電傳感器,每行的像素點數目高達9 216 個,像元大小為8.75 μm × 8.75 μm ,TDI積分級數為4,8,16,32,64,96,128 可選,行轉移速率為12 kHz.電荷讀出有向上和向下兩個方向可選,每個方向有6 個輸出端口,每個端口讀出速率為20 MHz,總速率為120 MHz,讀出像元電荷數目1 536 個。每個輸出端口有寄存器和放大器用來緩存和放大信號。TDICCD8091 內部結構包含有:光積分區域(垂直移位寄存器)、21行獨立區域(垂直移位寄存器)和水平移位讀出區域(水平移位寄存器),其中,21行獨立區域靠近水平讀出的3行為快速轉移區域,剩下的18行為慢速轉移區域,21行均被遮光材料遮擋。

TDICCD8091的外形圖如圖2所示。

2.2 TDICCD8091的時序要求分析

TDICCD8091積分級數的選擇由輸入端口VSW128-D(U)、VSW64-D(U)、VSW32-D(U)、VSW16-D(U)、VSW8-D(U)、VSW4-D(U)配合模擬開關控制實現。具體接法:例如當選擇向上32級積分時,VSW4-U、VSW8-U、VSW16-U接信號V3,VSW32-U接-3 V電壓,VSW64-U、VSW128-U 接+15 V 電壓,同時33~128 級的行轉移端口接+15 V電壓,水平移位讀出端口接+3 V電壓,1~32級的行轉移端口接信號V1、V2、V3,水平移位讀出端口接H1、H2、H3、H4.

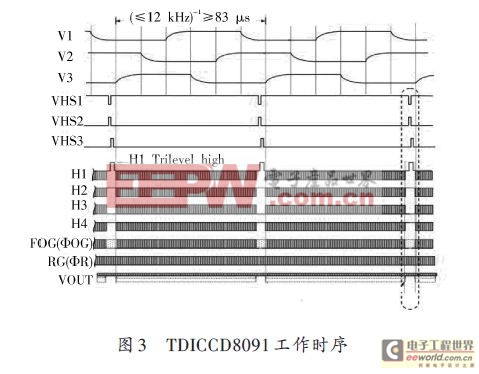

TDICCD8091正常工作所需要的時序信號如圖3所示。其中,V1、V2、V3為12 kHz占空比為50%的三相時鐘信號,時鐘高電平+15 V、低電平0 V,控制光積分區域和21 行獨立區域后18 行信號電荷的垂直移位;VHS1、VHS2、VHS3 為12 kHz占空比小于5%的移位時鐘信號,時鐘高電平+15 V、低電平0 V,控制前3行獨立區域信號電荷的垂直移位;H1、H2、H3、H4 為20 MHz占空比50%的四相時鐘信號,時鐘高電平0 V、低電平-5 V,控制每個端口1 536個像元電荷的水平移位讀出,同時,H1信號還控制像元電荷由垂直轉移向水平轉移的過度,此時高電平為+5 V;FOG為讀出時鐘信號,時鐘高電平+1 V、低電平-5 V;RG是復位脈沖信號,時鐘高電平+15 V、低電平+4 V,作用為在每個像元電荷讀出前,清除前一個像元殘余電荷,信號頻率20 MHz.這些時鐘的高低電平電壓值在硬件電路通過芯片EL7212驅動實現。

3 時序邏輯設計及仿真結果

3 時序邏輯設計及仿真結果3.1 時序程序設計

評論