信道模擬器的設(shè)計(jì)與FPGA實(shí)現(xiàn)(圖)

前言

無(wú)線(xiàn)通信是通信領(lǐng)域的一大分支,隨著數(shù)字信號(hào)處理能力的提高,數(shù)字無(wú)線(xiàn)通信逐漸成為無(wú)線(xiàn)通信的主流。數(shù)字無(wú)線(xiàn)通信系統(tǒng)設(shè)計(jì)的重要目標(biāo)之一是要系統(tǒng)具有很強(qiáng)的抗多徑干擾能力。通常,設(shè)計(jì)人員需要在實(shí)驗(yàn)室對(duì)無(wú)線(xiàn)信道可能存在的各種干擾(多徑、噪聲、同頻信號(hào)等)進(jìn)行虛擬實(shí)現(xiàn),以便對(duì)所設(shè)計(jì)系統(tǒng)進(jìn)行調(diào)測(cè)。多徑信道模擬器是進(jìn)行數(shù)字無(wú)線(xiàn)通信系統(tǒng)硬件調(diào)測(cè)不可或缺的儀器之一。無(wú)線(xiàn)移動(dòng)信道復(fù)雜多變,目前已有多種數(shù)學(xué)模型可供參考,本文針對(duì)無(wú)線(xiàn)移動(dòng)信道的基本模型,提出一種多徑信道模擬器的設(shè)計(jì)方法,給出了其基本結(jié)構(gòu)框圖,并對(duì)數(shù)字信號(hào)處理部分的fpga實(shí)現(xiàn)進(jìn)行了詳細(xì)闡述。

信道模型

在無(wú)線(xiàn)信道中,由于反射、散射和衍射等的存在,除了直射波之外,還會(huì)有信號(hào)通過(guò)不同的路徑沿不同的方向到達(dá)接收端,從而使信號(hào)產(chǎn)生時(shí)延擴(kuò)展;若接收終端處于移動(dòng)狀態(tài),各條信號(hào)支路還會(huì)具有不同的多普勒頻移,從而使信號(hào)產(chǎn)生頻率域彌散。典型的無(wú)線(xiàn)移動(dòng)信道二維沖擊響應(yīng)可表示如下[參考1]。

上式中,αk、 k、fdk和τk分別為第k條支路的歸一化幅度(衰減因子)、初始相位、多普勒頻移和傳播時(shí)延,τk>0,

,各條支路相互獨(dú)立,如圖1所示。

設(shè)發(fā)射信號(hào)為x(t)ej2πfct,x(t)為基帶信號(hào),fc為載波頻率,則接收信號(hào)y(t)為發(fā)射信號(hào)與信道沖擊響應(yīng)的線(xiàn)性卷積,

信道模擬器的設(shè)計(jì)與實(shí)現(xiàn)

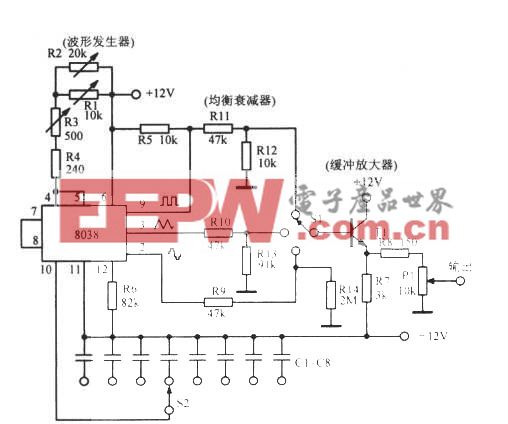

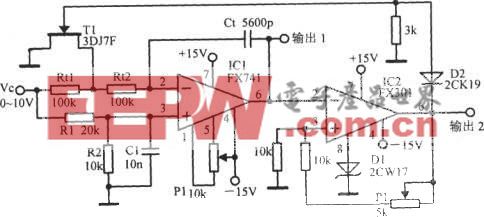

從上可知,要實(shí)現(xiàn)信號(hào)通過(guò)多徑信道的模擬,需要對(duì)信號(hào)進(jìn)行時(shí)延、(多普勒)頻移和衰減,并將各支路信號(hào)相加。因此多徑信道模擬器需要包含延時(shí)器、多普勒波產(chǎn)生器、衰減器、乘法器和混合器等單元。對(duì)射頻信號(hào)進(jìn)行處理時(shí),衰減較容易實(shí)現(xiàn),而延時(shí)和乘法運(yùn)算則實(shí)現(xiàn)難度大且精度不易保證。而數(shù)字電路在這方面卻有其獨(dú)到之處。因此,信道模擬器通常對(duì)信號(hào)進(jìn)行頻譜下搬移到基帶,然后對(duì)基帶信號(hào)進(jìn)行采樣,在數(shù)字域?qū)π盘?hào)進(jìn)行信道畸變處理,之后再經(jīng)過(guò)上變頻恢復(fù)成射頻信號(hào),如圖2所示。 圖2中,晶體振蕩器產(chǎn)生的正弦波通過(guò)頻率合成得到與輸入信號(hào)載波頻率基本一致的本地載波,混頻器對(duì)信號(hào)進(jìn)行上下變頻(正交解調(diào)和調(diào)制)。由于上下變頻用同樣的本地載頻,故可以保證輸出信號(hào)與輸入信號(hào)不存在頻率偏差。模數(shù)轉(zhuǎn)換器對(duì)信號(hào)進(jìn)行采樣,因?yàn)閿?shù)字部分實(shí)現(xiàn)容易,通常以幾倍的nyquist速率進(jìn)行采樣。虛線(xiàn)框內(nèi)部分則完成對(duì)數(shù)字基帶信號(hào)進(jìn)行通過(guò)信道的運(yùn)算,也就是下一節(jié)所要討論的內(nèi)容。

圖2中,晶體振蕩器產(chǎn)生的正弦波通過(guò)頻率合成得到與輸入信號(hào)載波頻率基本一致的本地載波,混頻器對(duì)信號(hào)進(jìn)行上下變頻(正交解調(diào)和調(diào)制)。由于上下變頻用同樣的本地載頻,故可以保證輸出信號(hào)與輸入信號(hào)不存在頻率偏差。模數(shù)轉(zhuǎn)換器對(duì)信號(hào)進(jìn)行采樣,因?yàn)閿?shù)字部分實(shí)現(xiàn)容易,通常以幾倍的nyquist速率進(jìn)行采樣。虛線(xiàn)框內(nèi)部分則完成對(duì)數(shù)字基帶信號(hào)進(jìn)行通過(guò)信道的運(yùn)算,也就是下一節(jié)所要討論的內(nèi)容。

一個(gè)好的信道模擬器,其信道沖擊響應(yīng)的時(shí)間分辨率一定要足夠高。信號(hào)的大延時(shí)在數(shù)字電路中通常用存儲(chǔ)器(ram或fifo)來(lái)實(shí)現(xiàn),而存儲(chǔ)器的讀寫(xiě)是與時(shí)鐘同步的,所以信道沖擊響應(yīng)的時(shí)間分辨率與數(shù)字信號(hào)處理單元的時(shí)鐘周期相等。為提高時(shí)間分辨率,需要對(duì)輸入信號(hào)進(jìn)行上采樣處理。上采樣后的信號(hào)在信道模塊與信道沖擊響應(yīng)進(jìn)行卷積得到經(jīng)過(guò)信道畸變的高采樣率信號(hào),運(yùn)算結(jié)果再經(jīng)下采樣濾波以適當(dāng)?shù)牟蓸勇瘦敵觯瑪?shù)模轉(zhuǎn)換電路將其恢復(fù)成模擬信號(hào)。

為方便信道參數(shù)設(shè)置,可通過(guò)單片機(jī)對(duì)頻率合成器和數(shù)字電路進(jìn)行配置。通過(guò)rs232串口電纜連接單片機(jī)和計(jì)算機(jī),可獲得良好的界面,通過(guò)計(jì)算機(jī)對(duì)信道模擬器進(jìn)行監(jiān)控。

數(shù)字部分的fpga設(shè)計(jì)與實(shí)現(xiàn)

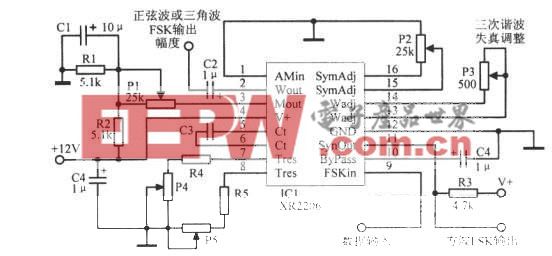

前已述及,信道模擬器數(shù)字部分需要對(duì)信號(hào)進(jìn)行上采樣、信道模擬和下采樣等,這幾部分運(yùn)算都需要大量乘法和加減法器,而且電路要工作在較高頻率的時(shí)鐘上,用通用的dsp難以實(shí)時(shí)完成。fpga基于硬件實(shí)現(xiàn),能滿(mǎn)足高速的要求,同時(shí)內(nèi)置鎖相環(huán)能提供靈活的時(shí)鐘倍頻功能[參考3],因此易于實(shí)現(xiàn)信道模擬功能。信道運(yùn)算的fpga實(shí)現(xiàn)如圖3所示。

圖3中,插值濾波、降采樣濾波和中間的信道部分都可視為有限序列與無(wú)限序列的線(xiàn)性卷積,宜采用fir(有限沖擊響應(yīng))濾波器直接型轉(zhuǎn)置結(jié)構(gòu)來(lái)實(shí)現(xiàn)[參考4]。其中延時(shí)器用來(lái)對(duì)信號(hào)進(jìn)行不同的延時(shí),乘因子產(chǎn)生器用來(lái)產(chǎn)生式(2)中各條支路的乘性項(xiàng)。接口電路用來(lái)完成fpga與單片機(jī)的通信,可用i2c結(jié)構(gòu)或其他簡(jiǎn)單通信協(xié)議來(lái)實(shí)現(xiàn)。fpga中主要模塊實(shí)現(xiàn)如下。

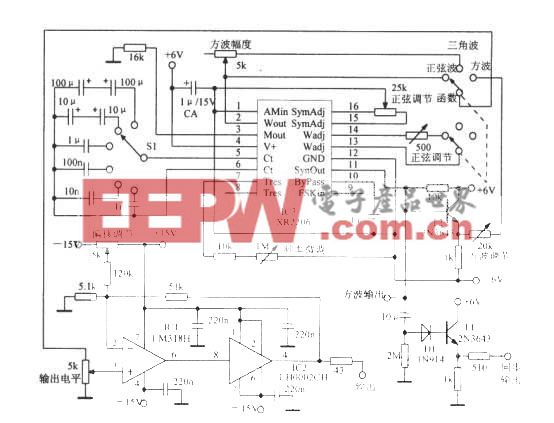

插值濾波器由并串轉(zhuǎn)換電路(用來(lái)對(duì)輸入序列進(jìn)行插零)和一個(gè)fir低通濾波兩部分組成,如圖4。

信道模擬器各條支路延時(shí)應(yīng)能靈活變化,因此圖3中延時(shí)器的時(shí)延量必須以時(shí)鐘周期為步長(zhǎng)可調(diào),這可采用雙口ram來(lái)實(shí)現(xiàn)。由于系統(tǒng)設(shè)計(jì)時(shí)并不太關(guān)心信號(hào)到達(dá)絕對(duì)時(shí)間,因此可令τ1=0對(duì)信道模型簡(jiǎn)化以節(jié)約存儲(chǔ)器資源,相應(yīng)地τk為第k條支路與第一條支路的相對(duì)時(shí)延差。

各信號(hào)支路的乘因子包括衰減因子和多普勒頻移因子兩部分。多普勒頻移因子由地址產(chǎn)生器(下圖的模2π加法器構(gòu)成)和查找表(rom)來(lái)實(shí)現(xiàn),查找表的輸出與衰減因子相乘得支路乘因子。

rom表的數(shù)據(jù)格式如下。

而整個(gè)rom表的大小可由實(shí)際所需(如fft長(zhǎng)度等)而定。當(dāng)然,rom表中的數(shù)據(jù)是被放大了215倍。如果所需rom表的存儲(chǔ)量很大,則可以只存儲(chǔ)(0,π/4)的數(shù)據(jù),而在(π/4,2π)范圍的則可以通過(guò)換算得到。

降采樣濾波器由低通濾波器和脈沖抽取電路組成。低通濾波器與插值器中的低通濾波器結(jié)構(gòu)相同,主要用來(lái)防止由于抽取帶來(lái)的頻譜混疊。脈沖抽取電路結(jié)構(gòu)和功能與插值濾波中的并串轉(zhuǎn)換相逆。

總結(jié)

針對(duì)典型的無(wú)線(xiàn)移動(dòng)信道模型,本文提出一種簡(jiǎn)單多徑信道模擬器的設(shè)計(jì)方法,給出了系統(tǒng)結(jié)構(gòu)原理圖和數(shù)字信號(hào)處理部分fpga電路實(shí)現(xiàn)框圖,并給出了fpga主要模塊的實(shí)現(xiàn)方法。在altera quartus平臺(tái)上的仿真表明,當(dāng)信號(hào)帶寬為10mhz、a/d轉(zhuǎn)換器工作在20mhz時(shí),一塊altera apex20k1000ebc652-1x單片fpga可以完成6徑的多徑運(yùn)算,時(shí)鐘頻率為40mhz,電路工作穩(wěn)定。若采用更大的fpga或?qū)S眉呻娐罚瑒t可實(shí)現(xiàn)更復(fù)雜的信道模型。進(jìn)行數(shù)字調(diào)制器設(shè)計(jì)時(shí),若在數(shù)模轉(zhuǎn)換前插入一片適當(dāng)規(guī)模的fpga,將上述信道模擬器數(shù)字處理部分嵌入其中,就可以在沒(méi)有昂貴的信道模擬器的情況下對(duì)所設(shè)計(jì)系統(tǒng)進(jìn)行信道實(shí)驗(yàn)。在altera apex20k600ebc652-1x上實(shí)現(xiàn)了對(duì)dvb-t調(diào)制器進(jìn)行恒參數(shù)信道模擬,測(cè)試表明其效果與專(zhuān)用信道模擬器相當(dāng)。

| 參考文獻(xiàn) 1 r.burow (t-berkom), k.fazel (dlr), p.hoeher (dlr), o.klank (dtb), h.kussmann (bosch), p.pogrzeba (tberkom), p.robertson (dlr), and m.j.ruf(bosch), “dvb-t and dmb in mobile environments,” ag3 (transmission concepts), task force dvb-dmb, february 1998 2 郭梯云,楊家瑋,李建東. 數(shù)字移動(dòng)通信. 人民郵電出版社. 2000 3 胡廣書(shū). 數(shù)字信號(hào)處理(理論、算法與實(shí)現(xiàn)). 清華大出版社. 1997 4 劉寶琴. altera可編程邏輯器件及其應(yīng)用. 清華大學(xué)出版社. 1995 |

評(píng)論