影響EMC的因素和降噪技術(shù)

電壓——電源電壓越高,意味著電壓振幅越大而發(fā)射就更多,而低電源電壓影響敏感度。

本文引用地址:http://www.104case.com/article/226966.htm頻率——高頻產(chǎn)生更多的發(fā)射,周期性信號產(chǎn)生更多的發(fā)射。在高頻數(shù)字系統(tǒng)中,當器件開關(guān)時產(chǎn)生電流尖峰信號;在模擬系統(tǒng)中,當負載電流變化時產(chǎn)生電流尖峰信號。

接地——對于電路設(shè)計沒有比可靠和完美的電源系統(tǒng)更重要的事情。在所有EMC問題中,主要問題是不適當?shù)慕拥匾鸬摹S腥N信號接地方法:單點、多點和混合。在頻率低于1MHz時可采用單點接地方法,但不適于高頻。在高頻應(yīng)用中,最好采用多點接地。混合接地是低頻用單點接地而高頻用多點接地的方法。地線布局是關(guān)鍵的。高頻數(shù)字電路和低電平模擬電路的地回路絕對不能混合。

PCB設(shè)計——適當?shù)挠∷㈦娐钒澹≒CB)布線對防止EMI是至關(guān)重要的。

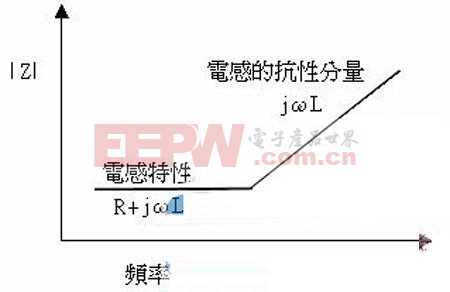

電源去耦——當器件開關(guān)時,在電源線上會產(chǎn)生瞬態(tài)電流,必須衰減和濾掉這些瞬態(tài)電流來自高di/dt源的瞬態(tài)電流導(dǎo)致地和線跡“發(fā)射”電壓。高di/dt產(chǎn)生大范圍高頻電流,激勵部件和纜線輻射。流經(jīng)導(dǎo)線的電流變化和電感會導(dǎo)致壓降,減小電感或電流隨時間的變化可使該壓降最小。

降低噪聲的技術(shù)

防止干擾有三種方法:

1. 抑制源發(fā)射。

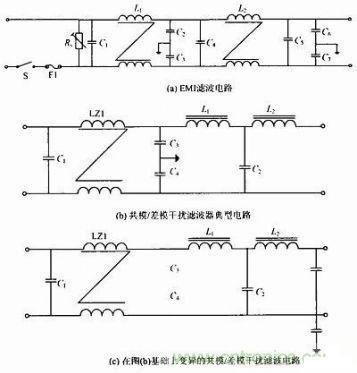

2. 使耦合通路盡可能地?zé)o效。

3. 使接收器對發(fā)射的敏感度盡量小。

下面介紹板級降噪技術(shù)。板級降噪技術(shù)包括板結(jié)構(gòu)、線路安排和濾波。

板結(jié)構(gòu)降噪技術(shù)包括:

* 采用地和電源平板

* 平板面積要大,以便為電源去耦提供低阻抗

* 使表面導(dǎo)體最少

* 采用窄線條(4到8密耳)以增加高頻阻尼和降低電容耦合

* 分開數(shù)字、模擬、接收器、發(fā)送器地/電源線

* 根據(jù)頻率和類型分隔PCB上的電路

* 不要切痕PCB,切痕附近的線跡可能導(dǎo)致不希望的環(huán)路

* 采用多層板密封電源和地板層之間的線跡

* 避免大的開環(huán)板層結(jié)構(gòu)

* PCB聯(lián)接器接機殼地,這為防止電路邊界處的輻射提供屏蔽

* 采用多點接地使高頻地阻抗低

* 保持地引腳短于波長的1/20,以防止輻射和保證低阻抗線路安排降噪技術(shù)包括用45。而不是90。線跡轉(zhuǎn)向,90。轉(zhuǎn)向會增加電容并導(dǎo)致傳輸線特性阻抗變化

* 保持相鄰激勵線跡之間的間距大于線跡的寬度以使串擾最小* 時鐘信號環(huán)路面積應(yīng)盡量小

* 高速線路和時鐘信號線要短和直接連接

* 敏感的線跡不要與傳輸高電流快速開關(guān)轉(zhuǎn)換信號的線跡并行

* 不要有浮空數(shù)字輸入,以防止不必要的開關(guān)轉(zhuǎn)換和噪聲產(chǎn)生

* 避免在晶振和其它固有噪聲電路下面有供電線跡

* 相應(yīng)的電源、地、信號和回路線跡要平行以消除噪聲

* 保持時鐘線、總線和片使能與輸入/輸出線和連接器分隔

* 路線時鐘信號正交I/O信號

* 為使串擾最小,線跡用直角交叉和散置地線

評論