采用0.13微米工藝實現低成本多處理器平臺

Zevio 項目架構師 Shinya Fujimoto 稱,他的 LSI 設計團隊必須在幾項約束下工作:建立一個通常模塊化的多處理器平臺,這樣 LSI 工程師可以通過塊的交換,快速創建出派生產品;采用成熟的 0.13 微米低功耗工藝技術實現 SoC,使成本保持在合理的低位,并且仍能達到性能與功耗目標;最后,在九個月內完成初始SoC平臺。

Fujimoto 說:“我們的背景是從事消費類ASIC。我們做過 PlayStation 和 PlayStation2 中的芯片,以及某些 iPod 設計,并且,在這些產品開發期間,我們注意到自己在重復調整芯片中非關鍵部分時花費了大量時間。這就是我們決定開發這一架構的原因。”

Fujimoto 稱,定義 Zevio 架構的第一步是要符合 VTech 和 Koto 的系統架構。他說:“我們試圖從客戶那里獲得盡量多的反饋乃至抱怨,以確定設計過程中的潛在瓶頸。”

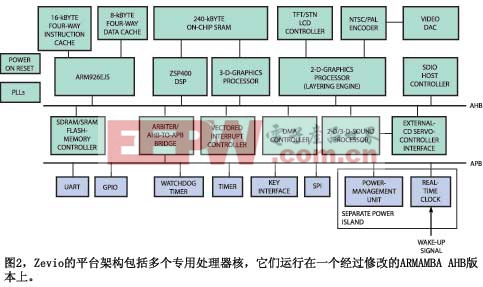

Fujimoto 稱,Zevio 不是一個典型的應用處理器(圖 2)。他表示:“我把它叫做一個異種多處理器。它有多個處理器,它們各不相同,但并行運行,每個處理器都專門完成一些自己擅長的任務。”

采用成熟的低功耗 0.13 微米工藝(從一家未披露名稱的臺灣伙伴處獲得)做設計實現,而不是采用 90 納米或 65 納米工藝,這有助于保持芯片的低成本,穩定電源管理,并且避免使用 DFM(可制造性設計)工具,所有這些都加快了設計進程。Fujimoto 稱,該芯片面向成本低于 100 美元的系統應用。“任何人都可以造出一款巨大的芯片,但有些人正在努力掙扎,尤其是那些無名的視頻游戲供應商,因為增加的芯片成本都要進入消費產品費用中。”

Fujimoto 指出,很多公司過快地跳到了最新最好的工藝,而他們本可以用更成熟和更穩定的工藝完成更多任務,例如用 0.13 微米工藝。“有些人不考慮 0.13 微米,認為它比較低端,但我們感覺可以通過智能工程化建立一個高端設計。客戶會從競爭者那里聽到很多有關高性能的故事,這個那個,全是一些浮夸的詞藻。但到最后,還是要歸結到花了錢就要獲得最好結果。”他堅持認為,0.13 微米工藝的成熟、成本、性能構成了最佳選擇。

LSI 希望 Zevio 成為一個可重用平臺,而不只是一片 ASIC,于是一個關鍵的要素是建立一個獨特的內核,可以將它與一系列 LSI 甚至第三處方供應商的內核結合起來。但是,架構規范的一個主要部分是新式圖形處理器內核設計。LSI 與 IP 供應商 Koto 合作開發 Zevio 的 3D 圖形處理內核。Fujimoto注意到,以前曾有多個 Koto 工程師在任天堂 GameBoy 設計團隊中工作。Fujimoto 說 LSI 在這個領域中幾乎沒什么閱歷,因此歡迎 Koto 的經驗。“他們為軟件開發人員需要的特性提供了大量經驗,幫助我們將很多這類技術訣竅轉化為硬件。”

Koto 的團隊完成了大部分規范工作,并對內核做了驗證,而 LSI 設計者則負責內核的設計和 RTL 實現。16位的3D圖形內核只需要 30萬個門,在 75 MHz 運行時功耗為20mW,每秒可以畫 150 萬個多邊形。

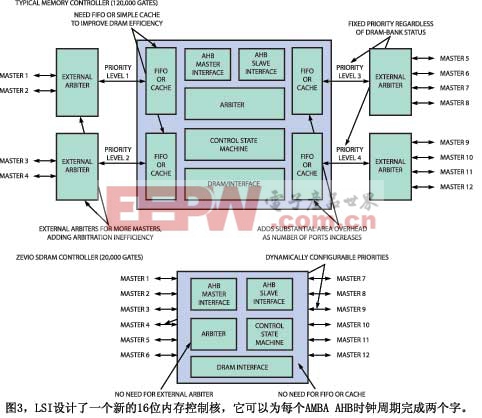

Fujimoto 指出,其它潛在的瓶頸是內存控制器及其與系統內存的接口。據芯片設計者講,雖然他們很容易做出一個32位總線接口,使之快速運行并得到所需性能,但 LSI 必須考慮如何從一個16位接口內存獲得相同的性能,以實現好的成本效益。

設計團隊必須從頭設計一個高效的控制器內核,它將采用一個16位 接口,并且考慮了效率仲裁(圖3)。Fujimoto 稱:“當查看一個16位接口時,我們關心的是獲得一個很好的時序窗口,以便向SDRAM 發送很多指令。”Fujimoto指出,控制器可以在每個總線時鐘周期取得兩個字。“我們申請了該技術的專利。它使我們能夠有效地用這些時序槽打開多個內存庫。”Fujimoto認為這一進展是架構中的關鍵創新。

Fujimoto 稱,接下來,團隊要查看有關的總線協議瓶頸。他們決定 采用流行的 ARM AMBA(先進微控制器總線架構)AHD(AMBA 高速總線)協議,但必須尋找克服AHB中部分低效的方法。他說:“我們必須看到,它無法突發式寫入隨機地址,并且不能規定足夠多的突發寫入。”為了解決這些問題,團隊自己編寫了 AHB 擴展,使內存控制器的效率翻了一倍。

在解決了規范階段的多數問題以后,設計團隊(其時有10個~15個設計與驗證工程師)開始作RTL設計。Fujimoto將他的團隊劃分為多個小組。他說:“一個小組專注于內存控制器,一個管圖形內核,另一個做音頻內核,其它小組負責整體集成。”

Fujimoto稱LSI的傳統方法是讓每個小組作設計,然后驗證各個單獨的塊,最后用仿真器將這些塊與系統中的其它核作驗證。但他的團隊這回首次采用了一種FPGA原型化系統,對圖形核、內存控制器和一個 LSI 開發的音頻處理器作驗證和軟、硬件的確認。

Fujimoto說:“在一個仿真環境中驗證這個設計可能會有太多的極限情況。這是我們第一次采用FPGA原型化系統。回想起來,我們應該在設計早期對各個內核多做一些驗證。”Fujimoto回憶說,一旦FPGA系統工作起來,事情就會進展得很快:“當我們遇到問題時,我們可以在連接到 FPGA 原型板的 LCD 屏幕上看到它。我們可以簡單地停下調試器,查看錯誤發生處的內部寄存器。”

小組還找到了一些后來證明是 FPGA 編程軟件中的錯誤(而不是設計的)。Fujimoto 說:“我們并不知道正在對付的錯誤是否是工具供應商造成的。FPGA 供應商提供的 FIFO 控制器也有問題。”

Fujimoto 指出,圖形小組在規范階段創建了一個圖形核的 C 模型。Fujimoto 說:“我們本可以用這個 C 模型作驗證,但要做太多工作才能更新 C 模型和 RTL。”他指出,如果你采用一種固定的規范,則可以用 C 模型方法,此時可以用 C 模型輸出來驗證 RTL 的輸出。但在 LSI 的案例中,當開始 RTL 時規格并未全部完成。他說:“一旦我們的 FPGA 系統開始運行了,我們就拋棄了 C 模型。”當設計在 FPGA 原型化系統上穩定下來時,小組還開始了驅動程序的初步開發。

原型電路板成為了驗證電路板的基礎,LSI 現在向希望用 Zevio SoC 開發其它系統的客戶提供這塊驗證板。當小組的 RTL工作穩定下來后,便運行一個試驗綜合和一個試驗布局,在初步布局的一部分中填充“空門”,以獲得有關區域與核尺寸的一個粗略思路。Fujimoto 稱他的團隊由Synopsys 作綜合,而由Magma 作布局和布線。

Fujimoto 稱,實驗布局對確定內存塊的正確布放尤其重要。設計中帶有 240 kB SDRAM。因此,Zevio 布局小組必須與 RTL 小組一起工作,將各個塊分解,以保證多個核能夠高效地訪問內存,而不致占用太多的布局空間。他說:“我們有這么大的內存,但我們同時允許圖形引擎和 DSP 訪問相同的內存。在功能寄存器中,我們指定了哪個核有權訪問內存,哪個將訪問,這樣我們就必須為 DSP 和圖形引擎預先定義某些段。”為實現這個目標,布局與 RTL 小組通過多次重復,確定了內存的最佳布局。最后,整個 Zevio SoC 包含200萬個門。

為保持設計低功耗,小組采用了一個多電壓閾值的 0.13 微米庫。Fujimoto說:“我們的想法是,將整體設計用所有低泄漏、低性能門作綜合,然后確定時序中的瓶頸和關鍵路徑,并將這些路徑轉換為高速門。”通過這個過程,團隊就能夠實現低泄漏與高性能晶體管的正確混合。

Fujimoto 稱物理驗證和設計出帶都相當順利。“原型硅片回來了,三天以后,我們所有的演示都在實際系統上運行起來。客戶能夠提前一周回家。采用成熟的技術,以及在過程的早期作驗證和預備工作,所有這些都得到了真實的回報。”

電路板開發的快速“結束”也意味著 VTech 的軟件小組可以快速地進入產品開發階段,最終使 VTech 在 2006 年圣誕期間及時將系統推向市場。

但是,VFlash 并非 Zevio 系列產品的唯一應用。事實上,Fujimoto 稱由于設計團隊創建的 SoC 模塊化,LSI 可以為其它客戶的應用作修改。Fujimoto 說:“我們平臺的設計目標是,只需六個月就能創建出派生的平臺。”

他指出,模塊化平臺使用戶能夠相當容易地將 ARM 核換成 MIPS 核,因為 LSI 同時擁有兩者的許可。用戶還可以換用一些外設核。LSI 正在為系統增加 USB 支持。Fujimoto 稱,下一代 Zevio 平臺也將很快用 DDR 代替 SDRAM。雖然 Koto 為平臺創建了最初的操作系統,但 LSI 正在擴展該平臺支持的操作系統數量,現在可以工作在 Linux OS 和 Windows CE 上。

Fujimoto稱,他的團隊已在 Zevio 上為一個匿名客戶完成了另一個項目。他說,硅片已經生產,但該客戶還沒有推出產品。

LSI 在 2004 年 12 月開始 Zevio 規范的制定過程,在 2005 年底啟動設計,在 9 個月后的 2006 年 9 月進入生產。

Zevio 項目是消費市場中成功的又一個案例,說明成功并非總是意味著采用最新最好的工藝技術實現最快的 SoC。LSI 的團隊在架構階段作了大量規劃,并在整個過程中做了一些創新的工程實踐,建立了一個比較強大而有性價比的平臺,幫助 VTech 抓住了市場窗口,LSI 也獲得了一個幫助其它客戶實現商機的通用工具。我們頗有興趣的是 LSI 會在多長時間內將 Zevio 繼續作為可行平臺,以及能為其它客戶創造出多少派生產品。

評論