卷積碼+QPSK的中頻調制解調系統的FPGA

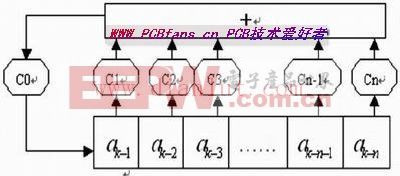

TB模塊從SPM中讀取當前時刻64條路徑的幸存信息,根據末端狀態可以找到相應的最大似然路徑在時刻t的幸存信息,從而找到t-1時刻最大似然路徑上的狀態。依此類推,直至找到最大似然路徑在t-L+1時刻的狀態,狀態的最高位即為譯碼輸出。

FPGA可以實現流水線操作,而各個模塊可以同時進行工作,所以需要控制模塊處理各個模塊間的時序關系。每個子模塊都有一個控制信號,使得輸入數據可以在各個模塊之間進行流水操作。

由于本方案是基于各個功能單元自上至下設計的,靈活性較大,稍加修改子模塊,便可以用于實現各種卷積碼的Viterbi譯碼器。

2.2 QPSK調制與解調的FPGA實現

QPSK調制模塊由成形濾波和上變頻兩部分組成。成形濾波具有兩個功能,即限帶和抗碼間干擾。成形濾波采用查表的方式實現,四倍內插,升余弦滾降。形成后的數據與NCO產生的本地載波進行上變頻運算。

QPSK解調的結構框圖如圖4所示。解調模塊由下變頻、低通濾波、根升余弦濾波和載波同步幾部分組成。I、Q兩路的調制信號先經過本地載波NCO下變頻,再通過低通濾波器LPF得到基帶信號。基帶信號需要進行相應的根升余弦濾波。由于本地載波與發端載頻之間有一定的偏差,所以要根據解調后的信號估計頻差并修改要地載波NCO的參數,實現載波同步。數據經過根升余弦濾波后進行差分解碼,解調后頭這入譯碼器單元。

綜上所述,系統主要功能都是在FPGA內完成的。本文選擇Xilinx公司的100萬門FPGA芯片XC2V1000,在ISE 6.2i環境下進行編程開發。系統的資源占用情況如表1所示。

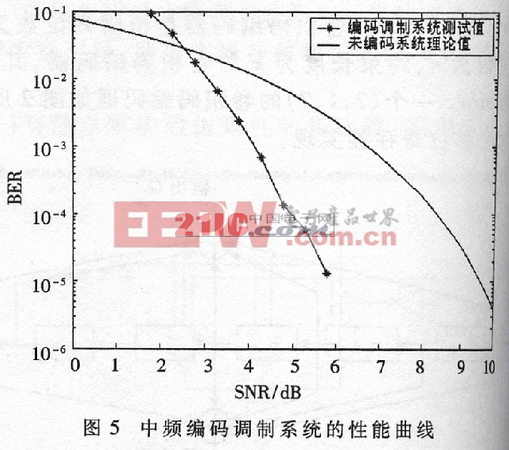

為了測試系統在噪聲下的誤碼率性能,在發端和收端之間引入噪聲源,在70MHz中頻上進行數據傳輸。使用誤碼率分析儀進行現場測試,獲得的測試誤碼率曲線如圖5所示。為了方便比較,圖中給出了未編碼傳輸系統的理想誤碼率曲線。由于定點實現、定時同步、載波同步等誤差因素,調制解調的實現損耗將近1dB;而viterbi譯碼的量化輸入和截短譯碼(本方案采用3比特量化和64步截短譯碼)帶來的實現損失約為1dB。(2,1,7)卷積碼的編碼增益約為5~6dB,所以測試誤碼率曲線與未編碼傳輸系統的理想誤碼率曲線之間的差距是3~4dB。換言之,本系統的實現增益為3~4dB。

綜上所述,本系統設計簡單、功耗低、性能良好,可在中頻范圍內進行高速數據的可靠傳輸。在不改變系統結構的情況下,稍加修改可廣泛應用于其它類型的編碼調制系統中。

評論