基于FPGA的多按鍵狀態識別系統設計方案

1 引言

按鍵作為普通的輸入外設,在儀器儀表工業設備和家用電器中得到廣泛應用。目前,按鍵輸入電路Ⅲ主要有2種:一種是非掃描方式可以判斷多鍵狀態(允許多鍵同時動作),但是不適用于大量按鍵情況,所需I/0端口多;另一種是掃描陣列方式,適用于大量按鍵,但不能多鍵同時動作。因此,需要開發一種既適合大量按鍵又適合多鍵同時動作,并能節省單片機(MCU)的口線資源的多按鍵狀態識別系統。這里提出一種利用FPGA的I/0端口數多和可編程的特點,采用VHDL語言的多按鍵狀態識別系統,實現識別60個按鍵自由操作,并簡化MCU的控制信號。

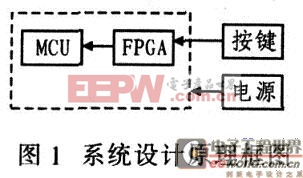

2 系統設計方案

FPGA是一種可編程邏輯器件,它具有良好性能、極高的密度和極大的靈活性,外圍電路簡單可靠等特性。因此,該系統設計是由MCU、FPGA、按鍵等部分組成。60路按鍵信號進入FPGA單元,以供數據采集;FPGA處理采集到的數據信號,編碼后寫入內部FIFO。MCU通過I/O端口提取FIFO中的數據。模塊通過電源接口向各個部分供電。其系統設計原理框圖如圖l所示。

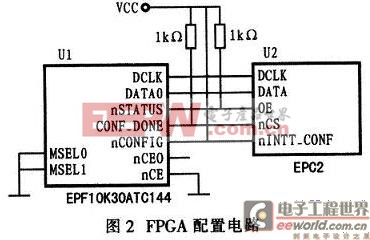

2.1 FPGA配置電路

FPGA采用Altera公司EPF10K30ATC144,該器件內核采用3.3 V供電,端口電壓為3.3V可承受5 V輸入高電平,其工作頻率高達100 MHz;有102個可用I/0端口,每個端口輸入電流最高達25 mA,輸出電流達25 mA;l728個邏輯單元(Les),12 288 bit的用戶Flash存儲器,可滿足用戶小容量信息存儲,完全滿足系統設計要求。

由于FPGA基于RAM工藝技術,該器件丁作前需要從外部加載配置數據,需要一個外置存儲器保存信息,采用可編程的串行配置器件EPC2.其供電電壓為3.3 V。OE和nCS引腳具有內部用戶可配置上拉電阻。FPGA的DCLK、DATA0、nCONFIG引腳信號均來自EPC2。系統上電后,首先FPGA初始化,nSTATUS、CONF_DONE置為低電平。nSTATUS置為低電平后復位,此時EPC2的nCE為低電平,因此選取EPC2,從而數據流從DATA引腳輸入到FPGA的DATAO引腳。配置完成后,FPGA將CONF_DONE置為高電平,而EPC2將DATA引腳置為高阻態。其FPGA配置電路如圖2所示。

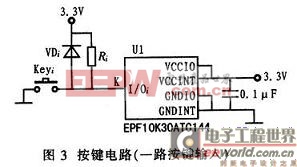

2.2 按鍵電路

圖3為一路按鍵電路,共60個按鍵(i=1~60)。由于外界環境復雜,按鍵引線長達6 m,保護二極管VDi:在外界干擾信號大于VCC時導通起到保護FPGA的作用。電阻Ri上拉限流,按鍵未閉合狀態下FPGA輸入引腳始終處于高電平。

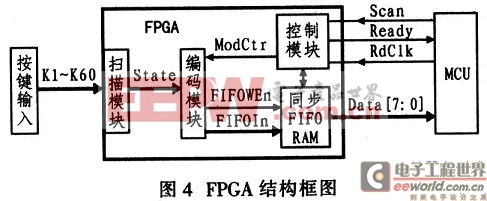

3 FPGA內部邏輯設計

FPGA內部功能分為掃描模塊、編碼模塊、控制模塊以及同步FIFO RAM模塊,如圖4所示。

圖4中,K1~K60為60個按鍵的輸入端,Scan為工作模式選擇信號,Ready為讀準備好信號,RdClk為讀時鐘信號,Data[7:0]為數據輸出,ModCtr為編碼模式控制信號,FIFOWEn為FIFO RAM寫使能信號,FIFOIn為FIFO RAM數據輸入,State為按鍵狀態掃描信號。其工作原理為:掃描模塊周期掃描按鍵狀態,其結果送入編碼模塊;編碼模塊根據模式控制信號ModCtr選擇編碼方式編碼,將其結果送入FIFO RAM;控制模塊產生對FIFO RAM的讀取控制信號;MCU可通過Readv、RdClk控制信號讀取Data[7:0]數據線上的按鍵編號和狀態數據。

評論