可編程芯片:拼合成一個模擬解決方案

不同的隱喻(metaphor)

芯片開發者傾向于向用戶隱藏起可編程芯片的結構,而代之以一種隱喻來虛擬化結構。他們希望,這種虛擬化對用戶更熟悉,對要解決的問題更有相關性。隱喻會隨硅片的結構,以及供應商對于客戶與客戶問題的觀點而變化。例如,在數字PLD的早期,供應商將一只PLD的內部描述為多組NAND門驅動大型NOR門輸入端,以后成為了表述邏輯功能的標準方法。

當FPGA出現時,其供應商初期將其描述為大型的邏輯單元陣列,每個單元都包括一些門和一個觸發器。這些隱喻都非常接近于芯片的實際電路。現在,FPGA已變得如此龐大,隱喻已更抽象。今天,看待FPGA的典型方法是將其當作一個空白單子,一個人在上面書寫RTL(寄存器傳輸級)邏輯,有便于布放分配的內存塊、DSP(數字信號處理)塊,以及高速I/O單元。沒人再嘗試使隱喻反映出電路情況。

從供應商為自己可編程模擬器件所選擇的隱喻中可以看到一種類似的差別。以Lattice為例,它對自己電源控制器IC的描述用詞接近于芯片上的實際元件:數字與模擬輸入、限幅比較器、一只ADC、一個可編程邏輯陣列,以及一組DAC。與之相比,Anadigm公司討論芯片時并不采用大多數用戶的術語,如電容、可配置放大器、階梯網絡或可編程模擬開關等。該公司描述的是模擬功能塊:運放、濾波器,等等。Anadigm公司首席運營官Simon Dickinson表示,當器件將成為一個較大設計中一分子時,該公司有時會鼓勵用戶把芯片想象成一個功能固定或具有多功能的黑盒子,而不管其中的內容。

一般來說,可編程模擬芯片的功能越專業,則隱喻就更貼切。不過,如果一種可編程結構是高度自適應的,則供應商可以采用兩種方案之一:應用與其下架構無關的隱喻,如Verilog-A或Spice網表,或隱藏可編程結構的隱喻,僅將其表述成一個參數化的固定功能芯片。隱喻的重要性在于,是它決定了用戶采用的設計方法,而不是其中的硅結構。一些案例可以說明這一點。

一些實例方法

Lattice公司主管電源控制器IC的營銷經理Shyam Chandra稱:“人們仍然采用分立芯片控制復位信號、看門狗時序,等等。我算了一下,(安森美的產品系列中)僅用于復位生成的就有400種芯片,市場上肯定有100種熱插拔控制器IC。”因此Lattice選擇了一種編程隱喻方式,使設計者像在使用一些較小型的固定功能芯片。

在開發設計規格時,Lattice產品的用戶會在數據表中搜索他們電路板上的處理器、內存、FPGA和其它器件,為每只芯片確定所需上電次序。對這些次序作編譯,就生成了控制器邏輯的完整狀態圖。但這是一種手工勞動,Chandra警告說:“大約75%的情況下,第一次工作是不正確的。人會出現錯誤,數據表規格中也經常會有灰色區域。”因此,Lattice公司提供了一種簡單的編程語言和波形仿真工具,用戶可以對次序作編碼,在不毀壞任何東西的情況下觀察其動作。當次序正確時,工具會配置Lattice芯片中的狀態引擎,使之可以驅動復位信號和為電路板提供順序供電的MOSFET門。同樣,Lattice公司還提供了一個輔助工具,用于設置芯片的微調與容限檢測電路。通過使用一個已知DC/DC轉換器的庫,軟件可獲取用戶的容限和電壓要求,設定片上比較器與DAC以及所需電阻值,同時監控轉換器的輸出和驅動微調輸入。

標準產品隱喻的概念超出了電源控制領域。在一個不同的市場中,Actel公司提供在Fusion系列FPGA上的可配置AFE(模擬前端)塊。該公司也同樣支持其可編程模擬段的配置,但也同樣懷疑用戶對板級仿真的興趣。該公司一名現場應用工程師Mark Nagel說:“我得說,我們只有不到一半的客戶會做任何一種全電路板仿真。在芯片級,我們確實提供了一種工具,它可以為模擬激勵生成波形,然后將其送入一個ADC模塊,提供用于FPGA邏輯ModelSim仿真的數字輸出。不過我們的AFE結構相當固定。對大多數人來說,我們的用戶傾向于先考慮分辨率、采樣率等的需求;配置AFE,并作嘗試。你可以用板上元件查詢AFE中的模擬結點,可以用芯片FPGA部分中的一個Synplicity嵌入邏輯分析儀查看數字輸出。”因此,用戶一般不用仿真工具研究AFE;他們只仿真數字邏輯部分。

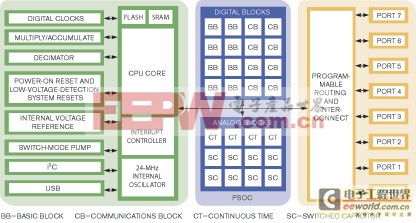

圖2,Cypress公司的PSoC包含一個微控制器,以及模擬與數字塊組成的可編程陣列。

另外一個例子來自Cypress半導體公司,其PSoC(可編程系統芯片)提供相對豐富的可配置模擬元件陣列,它與一個數字構建塊和一個微控制器核心緊密耦合(圖2)。Cypress硅結構的通用特性可以確定一種高級語言隱喻,以及一種綜合仿真設計流。不過該公司選擇了一個不同的方向。Cypress公司現場應用工程師Jason Baumbach解釋說:“我們的隱喻法是一個部件目錄,而不是一個可編程模擬陣列。給用戶展示數千個寄存器對他們沒有幫助。我們是提供一個‘用戶模塊’的目錄,”即芯片上可配置的模擬陣列部分。不過,它們對于用戶來說就是現成的模擬部件。用戶根據用戶模塊繪出其設計的模擬部分的邏輯,然后采用Cypress PSoC開發環境,就可以直接從邏輯圖進入到試驗板階段。Baumbach稱:“我們并未看到很多人在使用Spice或Matlab。多數情況下,他們嘗試做的模擬電路都相當簡單。”

評論