便攜式產品具有低功耗意識的FPGA設計方法

要減少RAM的功耗,除了對RAM的控制和時鐘信號進行門控制以外,還需要知道RAM的讀和寫分別對功耗的影響有多少。地址變化、讀寫順序、RAM級聯方式對功耗的影響。

對RAM進行讀操作涉及到:控制所存地址和控制鎖存、行的預譯碼電路、讀的列譯碼電路、行的最終譯碼電路、讀的列譯碼控制、傳感

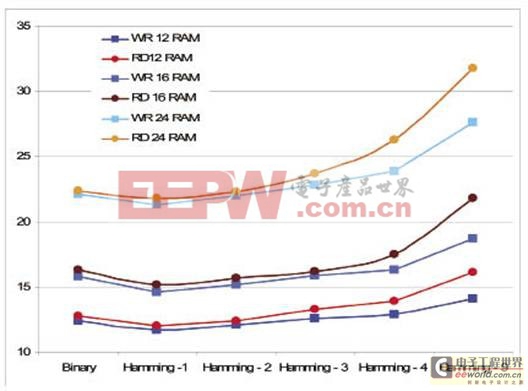

RAM的讀寫地址改變的方式,也會對功耗有不同的影響。連續操作地址之間的漢明距離越小,產生的功耗也越小。反之亦然。也就是說當前操作的地址和上次操作的地址之間變化的位數越少,所產生的功耗也會越小。

讀寫間隔操作和連續讀、連續寫操作相比,要產生多一些的功耗。從圖2中分別對12塊RAM、16塊RAM和24塊RAM做的測試結果看,同樣的操作條件下,RAM塊數越多,連續操作地址之間的漢明距離越長,功耗就越大。同樣的塊數和連續操作之間的漢明距離,寫-讀三次會比三次寫三次讀消耗的功耗要大。

圖2 寫讀操作順序vs.讀序列后跟寫序列操作

通過前面所述,我們可以通過調整RAM的訪問順序降低RAM的功耗。可能的話,對RAM少進行讀操作,盡可能一次多讀一些數據或者多寫一些數據,少一些讀寫操作之間的切換。如果在連續相同操作的地址之間,漢明距離能保持最小的話更好。也可以考慮在反向時鐘沿上對RAM進行讀寫操作,以降低RAM的峰值功耗。

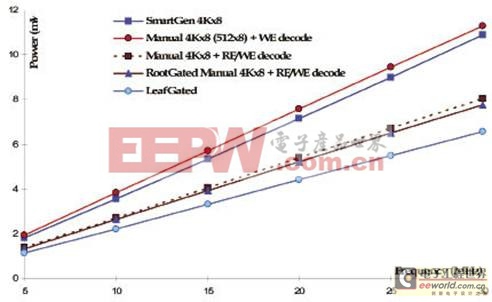

不同的RAM級聯架構所產生的功耗也不同。如果想獲得一個4K×4的RAM,有許多不同的實現方式。從圖3中可以看出,根據這些不同的實現方式,對每塊RAM的讀寫時鐘控制,進行門控制所產生的功耗是最低的。

圖3 根時鐘vs.葉時鐘vs.門控允許

評論