FPGA的時鐘頻率同步原理研究與設計實現

3 頻率補償算法在FPGA中的實現

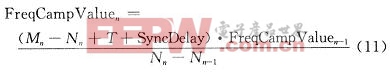

由式(4)和式(10)可得:

頻率補償就是在每個同步周期計算FreqCompValuen,FPGA提供了參數化的乘法器兆函數(1pm_mult)和除法器兆函數(1pm_divide),可以快速實現上述算法。原理如圖3所示,在每個同步周期同步信號的驅使下,鎖存器B和C分別鎖存當前時鐘讀數和上個同步周期時鐘讀數,同時將主時鐘讀數輸入到加法器A中,經過減法器E、F和乘法器G,以及除法器H后計算出新的FreqCompValuen,并在同步信號的驅動下,將其鎖存到鎖存器D中。由于中間的計算結果要經過一定的時鐘周期,所以鎖存器D的鎖存信號要延時一定的晶振周期。在本設計中延時50個FreqOsc,即在1μs的情況下就可以得到新的頻率補償值。

同步報文的傳輸延遲SyncDelay理論上是不變的,而實際上報文在傳輸過程中有抖動。參考文獻[3]對此進行了分析,并指出同步周期越長,報文傳輸延遲抖動的影響就越小,因此可以忽略不計。

4 實驗驗證

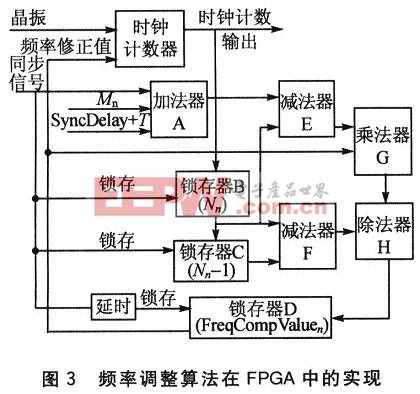

主時鐘采用50 MHz的有源晶振來實現,并將其作為固定時鐘;從時鐘采用30 MHz有源晶振,通過FPGA的鎖相環PLL將其頻率倍頻到60 MHz,然后1.2分頻,實現可調頻率的50 MHz時鐘。

讓主時鐘和從時鐘以一定的時間間隔產生中斷,并通過邏輯分析儀采樣中斷信號分析其偏差。由于系統時鐘的分辨率為20 ns,采用廣州致遠電子有限公司的邏輯分析儀LA1532,其最大采樣頻率為100 MHz,所以偏差測量精度可以達到10 ns。圖4(a)是未進行同步前兩個時鐘的偏差分析,X軸表示主時鐘和從時鐘的計時長度,Y軸表示主時鐘和從時鐘的計時偏差。從圖中可以看出兩個時鐘的偏差大概為5×10-6,即1 s內的偏差可以達到5μs。圖4(b)為同步后主時鐘和從時鐘偏差測量結果,共測量1 000次,其10 ms內同步偏差在±20 ns。X軸表示測量時間,Y軸表示主從時鐘同步偏差。圖4(c)為同步后兩個從時鐘偏差測量結果,共測量1 000次,其10 ms內同步偏差在±40 ns。X軸表示測量時間,Y軸表示從時鐘之間同步偏差。

結 語

基于時鐘頻率調整的時間同步方法,實現簡單,而且沒有復雜的軟件同步協議,占用較小的網絡帶寬就可以實現高精度的時鐘同步,在硬件上只需要低成本的FPGA支持。

評論