對FPGA中SPI復用配置的編程方法的研究

SPI(Serial Peripheral Inte

1 SPI配置介紹

1.1 Spantan-3E SPI配置流程

SPI方式是通過符合SPI接口時序的第三方SPI Flash對FPGA進行加載。它適合作為FPGA硬件結構的bit文件保存介質,如果應用軟件工程編譯后的代碼較小,保存在同一片SPI FLash中(即復用SPI Flash)無疑是可行的最廉價方案。

由于本沒計軟件工程規模較小,所以利用此復用SPI Flash方式對FPGA進行配置,既保存FPGA配置的bit文件,也保存應用軟件工程的bit文件。系統在上電或向PROG_B引腳發出低脈沖后,FPGA芯片經過一個初始化序列清空內部FPGA配置存儲器。此序列開始時,DONE和INIT_B引腳均轉為低。初始化完成后,INIT_B引腳轉為高,并采樣芯片的配置模式及變量選擇引腳。

SPI模式下,FPGA對變量選擇(VS[2:0])引腳采樣,以確定發出哪個SPI命令序列。當初始化之后發出INIT_B信號時,模式引腳和變量選擇引腳都必須處在正確的邏輯級,以確保正確采樣。

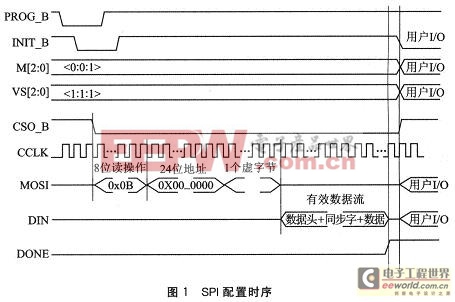

在變量選擇引腳選擇SPI命令集之后,FPGA將CSO_B選擇信號置為低,并且開始通過FPGA的CCLK引腳對SPI Flash存儲器進行時鐘控制。接著發出8位讀命令后跟24位起始地址0x000000和目標命令集的適量虛擬字節。FPGA從地址0開始讀取SPI Flash存儲器陣列,直到讀完所需的配置位數。如果從存儲器件讀取到有效比特流,則發DONE信號,以指示FPGA配置成功。圖1為SPI配置方式的時序。

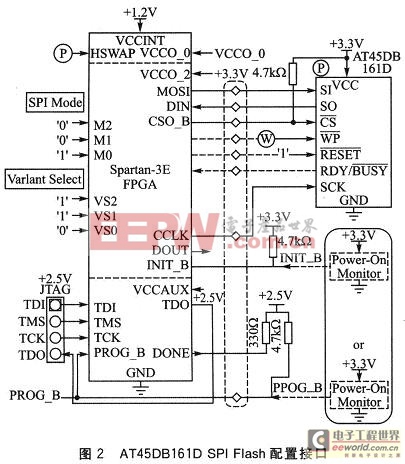

圖2是AT45DB161D SPI Flash的配置接口。這種配置方式只占用了FPGA芯片的4個引腳,而且配置成功之后,所有SPI引腳都成為可用的用戶I/O引腳,這就節省了FPGA的引腳資源。

評論