一種出租車計價器的FPGA設計方案及應用

2.3 緩沖器模塊

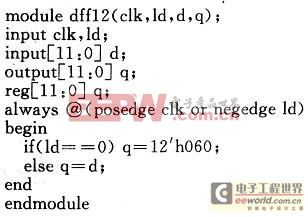

三位BCD碼加法器輸出的結果通過緩沖器以后,反饋到輸入端重新作為一個加數,在1km脈沖信號的作用下,每來一個脈沖就和單價相加,形成連續累加的功能。緩沖器還有一個控制輸入端LD,LD=O時,在1km脈沖的作用下,輸出起步價6元;LD=1時,在1km脈沖的作用下,輸出和輸入相等。緩沖器的Verilog HDL源程序如下:

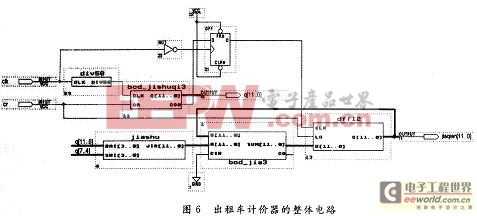

2.4 整體電路

將各個模塊按照輸入輸出關系連接成整體電路如圖6所示。

在整體電路中,clk為最原始的時鐘輸入端,cr為異步清零端,q[11..O]輸出里程,jiaqian[11..O]輸出乘客應付的費用。

3 系統仿真驗證

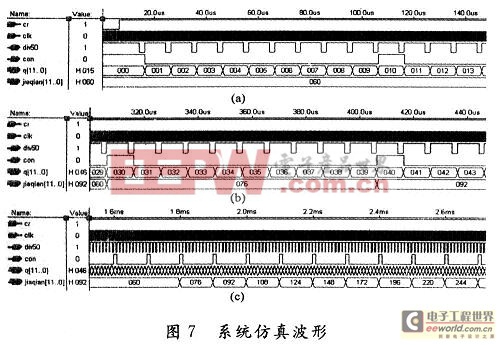

整體電路的仿真波形如圖7所示。

從系統仿真波形圖7(a)中可以看出,當清零端cr=O時,里程數立刻清零,乘客應付的費用顯示三位十進制數060(起步價6元),表示乘客剛上車。當清零端cr=1時,出租車開始行進,里程和費用都開始計數,里程顯示三位十進制數,前兩位為整數,第三位為小數,也就是每行駛100 m計一次數。

從系統仿真波形圖7(b)中可以看出,行駛到3 km時,費用由6元增加為7.6元,行駛到4 km時,費用由7.6元增加為9.2元,在3~7 km之間時,每行駛1 km增加1.6元。

系統仿真波形圖7(c)中顯示了每行駛1 km后,費用逐漸累加的情況。系統仿真波形完全驗證了預期的設計要求。

4 結 語

通過仿真驗證表明,本文所設計的出租車計價器能夠正常地顯示行駛的里程數和乘客應付的費用,符合預定的計費標準和功能要求。基于FPGA的設計,集成度高、設計周期短。尤其是當計費標準發生變化時,容易通過改寫Verilog HDL源程序來完成新的設計。

評論