一種基于FPGA/DSP的靈巧干擾平臺(tái)設(shè)計(jì)與實(shí)現(xiàn)

3 試驗(yàn)驗(yàn)證

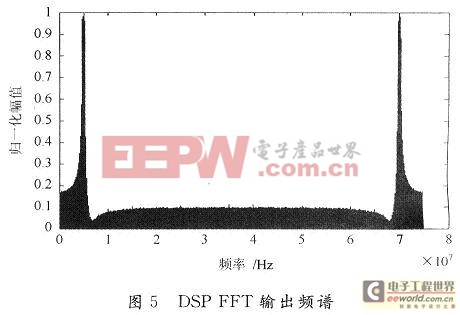

為了驗(yàn)證平臺(tái)能否在程序控制下正確工作,本文編寫了工作于DSP的8 192點(diǎn)FFT驗(yàn)證程序,實(shí)現(xiàn)對(duì)輸入信號(hào)的FFT變換。

試驗(yàn)中設(shè)置DDC為70 MHz混頻,DUC 70 MHz中頻輸出,輸入信號(hào)為75 MHz正弦波。在FPGA/DSP程序加載和DDC/DUC配置完成后,首先進(jìn)行ADC數(shù)據(jù)采集,把采集得到的數(shù)據(jù)存儲(chǔ)到SRAM中,DSP與SRAM進(jìn)行數(shù)據(jù)交互并在DSP中完成8 192點(diǎn)的FFT運(yùn)算,計(jì)算結(jié)果保存于SDRAM中,經(jīng)DMA方式讀取到上位機(jī)硬盤形成二進(jìn)制文件。同時(shí)將混頻后的5 MHz單頻信號(hào)從SRAM讀出上變頻到70 MHz輸出。試驗(yàn)結(jié)果如圖5、圖6所示。

由圖5可知,DMA輸出的FFT結(jié)果顯示處理的下變頻信號(hào)為5 MHz,等于預(yù)期值;圖6顯示5 MHz單頻信號(hào)經(jīng)上變頻后輸出為70 MHz中頻

4 結(jié) 語(yǔ)

根據(jù)靈巧干擾平臺(tái)功能要求,設(shè)計(jì)了基于FPGA/DSP的硬件平臺(tái),采用Verilog HDL及模塊化方法設(shè)計(jì)了硬件平臺(tái)的控制軟件。試驗(yàn)結(jié)果表明,靈巧干擾平臺(tái)構(gòu)成合理,硬件設(shè)計(jì)、軟件設(shè)計(jì)可靠,滿足了靈巧干擾平臺(tái)的功能要求,為靈巧干擾技術(shù)研究提供了硬件平臺(tái)支持,該平臺(tái)已成功應(yīng)用于工程項(xiàng)目。

評(píng)論