采用FPGA設計SDH光傳輸系統設備時鐘

采用銣鐘作為測試時鐘基準源。基準時鐘送TSP8500進行跟蹤,同時送時間間隔分析儀。

TSP8500的系統時鐘sysclkout的參考源,通過CPU接口選定為時鐘基準源送來的2.048MHz時鐘。由于系統時鐘sysclkout輸出為38.88MHz,不便于用時間間隔分析儀進行測試,所以采用外同步時鐘ext_clk_out接口輸出2.048MHz時鐘送時間間隔分析儀進行TIE曲線的測試;而ext_clk_out時鐘的參考源,則通過CPU接口選擇sysclkout時鐘。

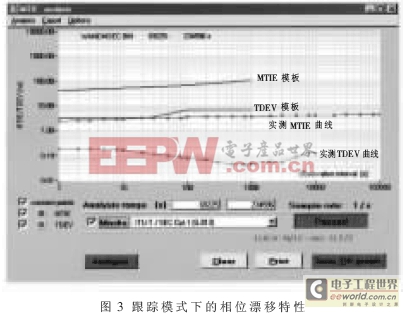

在跟蹤模式下,圖2中的開關K閉合,測試24小時后得到的MTIE/TDEV曲線,如圖3所示。

從圖3的測試結論來看,TSP8500跟蹤模式下的相位漂移特性滿足ITU-T G.813建議要求。

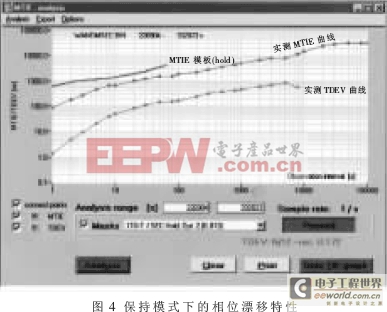

跟蹤24小時后,將圖2的開關K斷開,TSP8500的系統時鐘自動進入保持工作模式,繼續用時間間隔分析儀表測試24小時,得到保持模式下的MTIE/TDEV曲線,如圖4所示。

從圖4的測試結論來看,TSP8500芯片在保持模式下的相位漂移特性也滿足ITU-T G.813建議要求。

采用單片FPGA實現的SEC芯片TSP8500,輸出時鐘滿足其在SDH設備中應用的要求,各項時鐘性能指標完全滿足ITU-T G.813的相關建議要求。TSP8500芯片已在國內某著名通訊設備廠商開發的SDH設備中得到應用。

另外,TSP8500芯片所采用的FPGA,其成本低于10$,遠低于商用SEC芯片的價格,且功能可靠,具有相當高的性價比,有望得到更大規模的商用。

評論