基于FPGA和USB2.0的高速CCD聲光信號采集系統

0 引 言

在現代通信和雷達領域中,寬帶、高增益、實時并行處理是現代接收機的重要標志。因而,這種具有高速并行處理能力和特有的大帶寬性能的聲光處理系統具有巨大的潛在優勢。以聲光器件為基礎的接收機除了具有寬帶、高增益、實時并行處理等特點外,還具有容量大,體積小,功耗低等優點。因而,采用聲光信號處理技術解決帶寬、高增益和實時并行處理問題具有重要意義,聲光信號的采集系統的設計是整個聲光系統關鍵之一。這里設計了一個基于FPGA和USB 2.0的高速CCD聲光信號采集系統,為聲光信號采集提供了硬件平臺。

1 系統概述

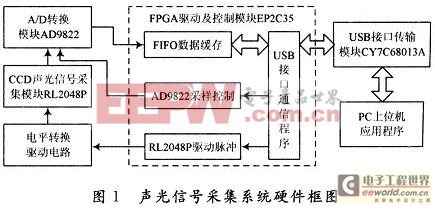

聲光信號采集系統框圖如圖1所示。系統主要由CCD聲光信號采集模塊、A/D轉換模塊、FPGA驅動和控制模塊及USB接口傳輸模塊四部分組成。

系統上電后,USB設備按照上位機的命令完成對。FPGA數據采集參數的初始化設置及采集控制。RL2048P在驅動時序的嚴格控制下工作,采集的

2 系統各模塊設計

系統各模塊設計為:

FPGA驅動及控制模塊 系統采用Altera公司的CycloneⅡ系列。EP2C35F672C6芯片,具有高性價比及豐富的邏輯資源,可滿足系統的要求。有4個PLL,33 216個LE,48 KB存儲器資源,可以配置成各種模式的ROM,RAM及。FIFO,35個18×18的專用乘法器。FPGA的主要功能是產生RL2048P驅動時序,控制AD9822采樣及對其寄存器實現串行編程,內部配置FIFO緩存數據以及與USB接口通信,并傳輸數據到上位機中。

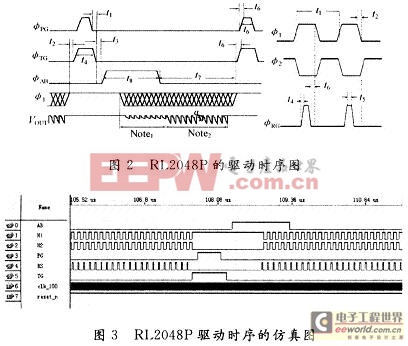

CCD聲光信號采集模塊 選用PerkinElmer公司的RL2048P線陣CCD。該芯片主要用于高速信號采集,2 048個有效像元,具有高靈敏度、大動態范圍、寬光譜范圍等特點,最高工作頻率為40 MHz,該系統設計為10 MHz。EP2C35的時序驅動輸出是3.3 V的LVTTL電平,不能直接驅動RL2048P(多電平要求)。因此,使用DG642和74FCT16244TV芯片完成電平轉換,增強驅動能力。圖2為RL2048P驅動時序圖;圖3為使用Verilog HDL編寫驅動時序的QuartusⅡ仿真。由比較可見,設計完全能滿足時序的嚴格要求。

評論