一種基于FPGA的永磁同步電機控制器的設計

摘要:提出一種基于FPGA的永磁同步電機控制器的設計方案,該設計可應用于具有高動態性能要求的永磁同步電機伺服控制系統。為提高伺服控制系統的實時性,簡化電路及節省成本,該系統設計采用Ahera公司生產的CycloneIII EP3C25Q240C8型FPGA器件實現電機控制器。嵌入NiosⅡCPU軟核配合片內硬件乘法器及可編程邏輯門陣列,實現軟硬件協同工作。通過QuartusⅡ軟件自帶的SignalTaplI嵌入式邏輯分析儀進行板上調試驗證,得到帶有死區輸出的PWM波形。該PWM波形可用于電機驅動。

1 引言

國內普遍采用TM320系列的DSP器件作為永磁同步電機控制系統的主控制器,因CPU負載過重導致系統實時性降低的問題日益顯著。采用具有并行工作特性的FPGA器件作為主控制器能夠提高系統實時性。因此,這里給出一種基于FPGA的永磁同步電機控制器設計方案。

FPGA器件內嵌NiosⅡCPU軟核的SoPC是Altera公司首創的SoC解決方案。將SoPC應用到電機控制中,是當前的研究熱點。FPGA依靠硬件邏輯門工作,NiosⅡ處理器依靠執行軟件程序工作。而在電機控制中實現軟硬件協同工作則是設計的難點和創新之處。本設計需要特別注意軟硬件協同工作的時序控制。軟硬件之間信號的交換需按嚴格時序進行控制。

2 片上系統規劃

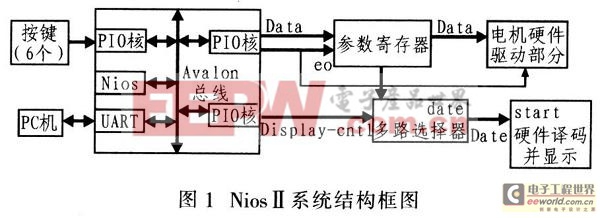

片上系統功能總體規劃為電機硬件驅動和NiosⅡ系統模塊兩部分,前者主要完成速度外環,電流內環的雙閉環運算;而后者主要完成按鍵輸入、LED數碼管顯示、電機驅動器參數設置和傳輸以及上位機通信。

3 系統硬件設計

3.1 NioslI系統模塊

3.1.1 Nios lI系統模塊的設計

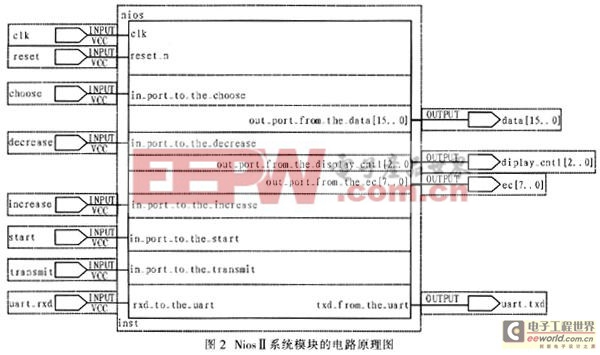

在QuaauslI的SoPC builder中調出nioslI軟核。調用4個用于輸出的PIO核,掛接到Avalon總線上,作為信號輸出I/O端口,這4個PIO核分別是start(啟動電機信號),Data(16位,電機參數值),ec(8位,參數寄存器使能信號),choice(3位,多路選擇信號)。調用6個作為輸入的PIO核用以按鍵輸入。設置中斷掩碼寄存器為中斷有效,邊沿捕獲寄存器為上升沿檢測。按鍵經FPGA引腳,用戶設計硬件防抖動后,產生一個上升沿信號,啟動NioslI處理器中斷,執行相應中斷功能。調用異步串口UART內核,實現與上位機通信,設置其波特率同定,UART通過中斷請求實現數據通信功能。圖1和圖2分別給出Niosll系統結構框圖和其電路原理圖。

評論