基于IPTV系統中的FPGA供電問題解決方案

目前越來越多的家用電器從低速的撥號上網向寬帶互聯網接入或互聯網協議電視(IPTV)轉移,尤其是IPTV有望在中國獲得快速的發展。比較而言,IPTV的基礎設施成本相當低,因為這種方法不需要銅軸電纜,而是采用DSL或寬帶鏈接和機頂盒將節目流傳送到家用電器。

現在的可編程門陣列(FPGA)已經被證明是這種平臺的理想選擇,因為它們提供了快速改變市場需求的靈活性。FPGA的電源需求通常很復雜,因為FPGA有多達三種供電要求,為了實現可靠的系統性能,必須對這些要求排序。

內核電壓

內核電壓軌通常設定成VCCINT,為FPGA邏輯供電。要求的電流從幾百毫安到幾十安培,具體大小取決于時鐘頻率和所用的門數。因為該負載是呈高度容性,內核電壓電流要求可能在開始的時候很高。FPGA內核對瞬態響應的要求很嚴格,內核電源電壓必須緩慢增加并且常常要求在固定的時間長度內上升到穩定的電壓。例如,Xilinx公司的Virtex-4必須讓VCCINT電源在0.2ms和50ms之間上電。

I/O電壓

I/O電壓(VCCIO)通常要求的電壓軌是3.3V、2.5V、1.8V或1.5V。I/O標準可以由FPGA中的I/O模塊獨立設置,因此一個FPGA就有可能存在一個以上的I/O電壓。I/O電流要求取決于所用的I/O數量和時鐘速度。通常,I/O電流要求低,范圍在幾百毫安到3A。

輔助電壓

輔助電壓(VCCAUX)要求電源具有高電源抑制比(PSRR),因為電源直接與數字時鐘管理(DCM)相連。如果電源噪聲被容許耦合到DCM,將可能影響到系統的性能。

雖然I/O和輔助電壓不需要按照特別的順序上電,但是,FPGA制造商常常要指定內核和I/O的上電順序或跟蹤該順序。不指定上電順序或不跟蹤上電順序所面臨的后果是常常會對系統中的器件造成不可挽回的破壞。FPGA、PLD、DSP和微處理器通常在內核與I/O電源之間放置二極管作為ESD保護元件。如果電源違反了跟蹤要求并超過了保護二極管的正向偏置,那么該器件就可能被損壞。

解決方案

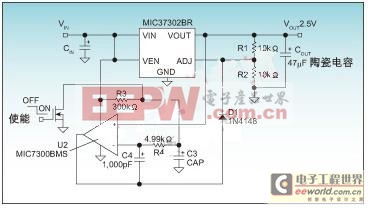

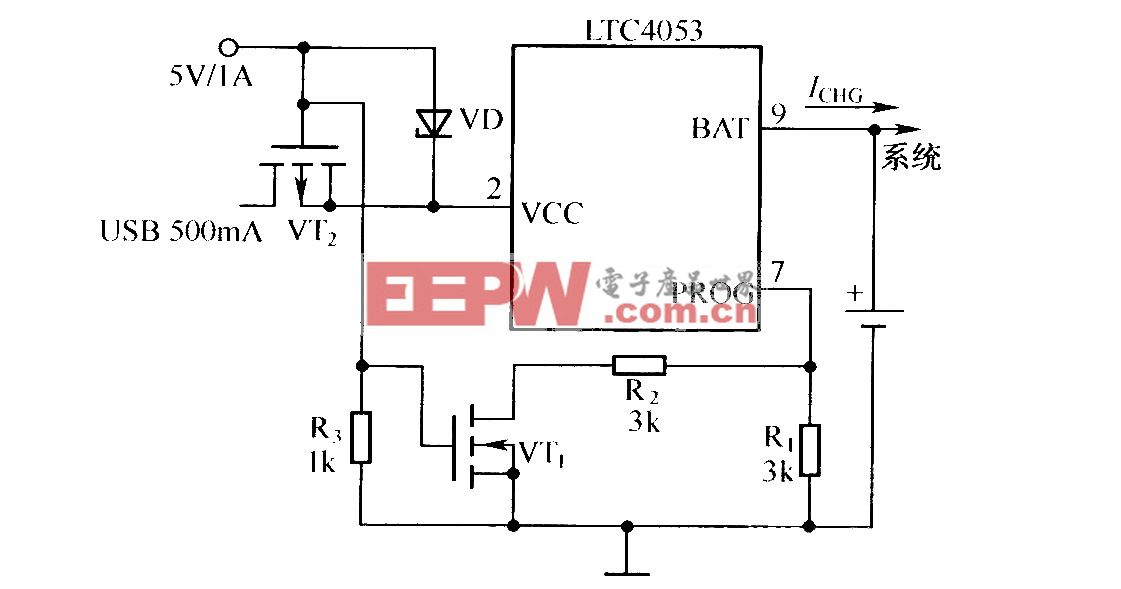

為說明FPGA供電要求的復雜性,以在固定時間段對VCCINT上電的要求為例。為了保證由上下限控制的2ms到50ms之間的上電時間,要實現如圖1所示的電路。

圖1:MIC37302和分立電路確保受控的斜率和時序

對內核和I/O電源的上電排序或上電順序的跟蹤,增加了電源管理電路的復雜性和成本。為克服這個問題,設計工程師需要一種不增加外部元器件而滿足所有這些需要的器件。這種產品的一個例子就是Micrel公司的MIC68200 LDO適用于各種板上電源" target=_blank>LDO,它把上升速度控制、上電排序和跟蹤等功能集成到一個3×3mm的MLF封裝之中。

評論