FPGA技術在雷達信號模擬器中的應用

2.2 各種體制雷達信號的實現方法

簡單脈沖調制和重頻調制雷達信號的實現方法比較簡單,這里只描述頻率捷變雷達信號、線性調頻雷達信號和相位編碼雷達信號的實現方法,并給出相應的QUARTUS仿真結果。

(1)頻率捷變雷達信號

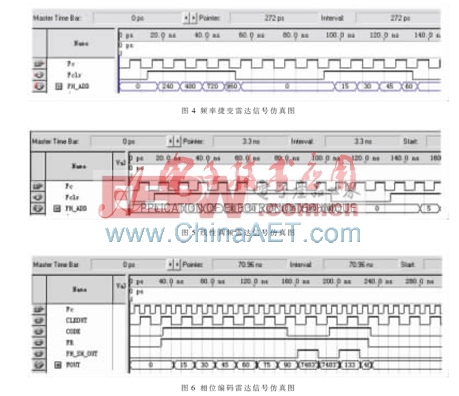

頻率捷變信號與常規雷達信號相比,只是頻率發生了變化,而其他參數不變,其既可以實現脈間捷變,也可以實現脈組捷變。當脈間捷變時,只需要在每個調制脈沖期間設置不同的頻率控制字即可;脈組捷變是在一組脈沖周期內為一個頻率控制字,而在另一組脈沖周期內為另一個頻率控制字,根據頻率捷變數量循環使用頻率控制字。圖4所示是只有2個頻率的脈間捷變信號的相位累加器輸出的仿真結果,為了便于觀察,2個頻率對應的頻率控制字分別定為240和15。

(2)線性調頻雷達信號

產生線性調頻是在普通的DDS核前面增加了一級頻率累加器,定期改變頻率控制字,從而改變輸出信號的頻率。如果頻率增量字是一個恒定的值,則輸出信號為線性調頻信號;如果頻率增量字是一個變化的值,則輸出信號為非線性調頻信號。圖5所示為線性調頻信號的仿真結果。

(3)相位編碼雷達信號

圖6所示為5位二相編碼信號的仿真結果,其編碼順序是“+ + + - +”,其相位分別在“+ → -”和“-→ +”時發生180°的相位跳變。

本文基于軟件無線電的思想,通過在FPGA中實現一個完全的DDS內核,實現多種雷達信號的產生,產生的雷達信號完全能夠滿足各種雷達信號處理實驗的要求。文中討論了各種信號獨立產生的方法,如果將DDS內核中的正弦表設計成雙端口存儲器,還可以實現任意波形和多種組合波形的產生。

參考文獻

[1] 徐袆,姜暉,崔琛.通信電子技術[M].西安:西安電子科技大學出版社,2002.

[2] 何立民.單片機應用系統設計[M],北京:北京航空航天大學出版社,2002.

[3] 宋萬杰,羅杰,吳順君.CPLD技術及其應用[M].西安: 西安電子科技大學出版社,2000.

[4] 王誠,吳繼華,范麗珍,等. Altera FPGA/CPLD 設計[M]. 北京:人民郵電出版社,2005.

[5] 奧本海姆 A V, 謝弗R W. 離散時間信號處理[M]. 西安:西安交通大學出版社,2001.

評論