FPGA技術在雷達信號模擬器中的應用

摘 要: 基于FPGA的各種雷達信號產生方法,介紹了在FPGA中實現直接數字頻率合成器(DDS)以及提高輸出信號質量的方法,編程實現了頻率捷變、線性調頻以及相位編碼等雷達信號的產生。仿真結果表明,該方法能靈活地產生多種雷達信號,且質量較好。

雷達信號模擬器需要模擬簡單脈沖調制、重頻調制(重頻參差、重頻抖動和重頻滑變)、載頻調制(線性/非線性調頻、頻率捷變)和相位調制(相位編碼)等樣式的雷達信號[1]。傳統的實現方法是采用直接數字合成器DDS實現。通過對DDS相關參數產生對應的雷達中頻信號,其優點是產生的信號質量比較好,缺點是系統控制繁瑣、模擬的雷達信號參數相對固定、缺乏足夠的靈活性,對于非線性調頻和相位編碼信號很難達到令人滿意的效果。

本文基于軟件無線電的思想,采用FPGA實現DDS功能,通過控制DDS參數,在1片FPGA中實現了各種雷達信號的模擬。

1 DDS基本原理

DDS由相位累加器、只讀存儲器(ROM)、數模轉換器(DAC)和低通濾波器(LPF)組成。DDS的關鍵部分是相幅轉換部分,根據相幅轉換方式的不同,DDS大致可分為兩大類:(1)ROM查詢表法。ROM中存儲有不同相位對應的幅度值,相位累加器輸出對應的幅度序列,實現相幅轉換;(2)計算法。對相位累加器輸出的相位值通過數學計算的方法得到對應的幅度值,實現相幅轉換,這里的計算方法有拋物線近似法、CORDIC法等。

對于查詢表法,ROM里存儲了2N個點(一個周期)。工作過程如下:在時鐘脈沖fc的作用下,頻率控制字K由累加器累加得到相應的相位碼,相位碼尋址ROM進行相位/幅度變換輸出不同的幅度編碼,相當于在ROM里每隔K個點取出一個點,再經過數模轉換器DAC得到相應的階梯波,最后經低平滑濾波器對階梯波進行平滑,即得到由頻率控制字K決定的連續變化的模擬輸出波形,輸出頻率fout為:

式中,K為頻率控制字,N為相位寄存器字長。輸出頻率由頻率控制字及相位寄存器字長決定。

理想情況下,由于采樣的原因,輸出信號頻譜存在一些雜散,譜線呈辛格函數形狀。DDS輸出信號雜散分量較大的主要原因有以下幾點:一是相位截斷效應;二是存放在ROM中的波形幅度存在量化誤差;三是DAC的非理想特性。在DDS中,為了得到高的頻率分辨率,相位累加器的字長一般較大,而只讀存儲器ROM的容量有限,通常位輸出中只有高A位用來尋址ROM,從而產生相位截斷誤差,而DAC和ROM正弦波幅度字長也是有限的,同時,在DAC轉換過程中總存在如微分線性誤差等誤差,這樣就產生了量化誤差和DAC的非理想特性誤差。

2 基于FPGA的雷達信號模擬器

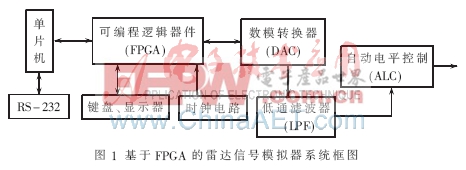

基于FPGA的雷達信號產生器系統框圖如圖1所示。系統主要由單片機、FPGA、模數轉換器、低通濾波器、自動電平控制、RS-232通信接口、時鐘電路以及人機接口等部分組成。單片機完成系統控制、人機交互控制以及與上位計算機的信息交換[2]; FPGA實現DDS的模擬以及其他邏輯的產生[3-4];模數轉換器將數字信號轉換成模擬信號,經低通濾波器濾波后獲得良好的波形信號;為了提高信號產生器帶負載的能力,自動電平控制部分保證輸出信號幅度在接入不同負載時變化不致太大。

系統工作時,單片機將由RS-232接口接收到的或由鍵盤設置的信號參數寫入FPGA,在FPGA中實現的DDS內核根據設置的參數產生相應的數字波形,經D/A轉換、低通濾波和電平控制后輸出。

評論