一種基于FPGA和單片機的頻率監測系統設計

O.引言

本系統利用單片機和FPGA有效的結合起來共同實現等精度頻率測量和IDDS技術,發揮各自的優點,使設計變得更加容易和靈活,并具有頻率測量范圍寬、產生的波形頻率分辨率高及精度大等特點。

系統方便靈活,測量精度和產生的波形分辨率高,能適應當代許多高精度測量和波形產生的要求,可以在各類測量系統和信號發生器中得到很好的利用,頻率測量在電路實驗、通訊設備、音頻視頻和科學研究中具有十分廣泛的用途。等精度測量技術具有廣闊的應用前景,由于其性能的優越性,在目前各個測量領域中都可以發揮著很好的作用,特別是在海洋勘探,太空探索以及各類實驗中都得到了應用。

1.DDS信號發生器的實現

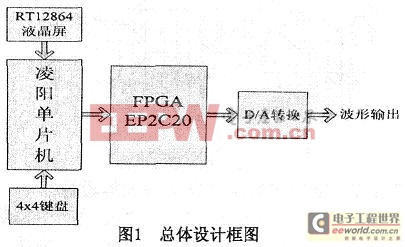

使用FPGA與單片機相結合的方式構成DDS信號發生器的核心部分,這是一種從相位概念出發直接合成所需波形的一種新的全數字頻率合成技術。其中FPGA完成相位累加、波形地址查找及波形輸出等功能,凌陽16位單片機實現頻率控制字的輸入和液晶顯示部分。FPGA與單片機通過串行輸入并行輸出的方式進行通信。其總體設計框圖如圖1所示。

1.1 DDS產生原理

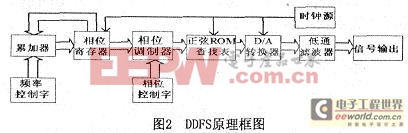

圖2是一個基本的DDFS結構框圖。DDFS 以數控振蕩器的方式,產生頻率可控制的正弦波、方波、三角波,電路包括了基準時鐘源、相位累加器、相位調制器、波形ROM查找表、D/A轉換器和低通濾波器等。頻率控制字N和相位控制字M分別控制DDS所輸出的波形的頻率和正弦波的相位。

1.1.1 頻率部分

一個N位字長的二進制加法器的一端和一個固定時鐘脈沖取樣的N位相位寄存器相連,另一個輸入端是外部輸入的控制字M。這樣在每一個時鐘到來的時候,前一次相位寄存器中的值和當前的M值相加,作為當前相位寄存器的輸出。控制字M決定了相位增量,加法器不斷的對相位增量進行線性累加。當產生一次溢出后,完成一個周期性動作,即DDFS合成信號的一個頻率周期。

設基準時鐘信號為fclk,分頻值為N,累加器位數為M,相位累加器步進值為L,根據公式:

設最高頻率為20KHz,步進為20Hz,因此累加器位數至少為10位(210=1024>20000/20)。為了保證在最高頻率下的波形在一個周期內至少有32個點,因此累加器至少有lO+5=15位。

取晶振頻率32.768MHz,可得

![]()

評論