一種基于FPGA的多路視頻通道控制系統設計

2.2 雙口RAM及開關信號編碼設計

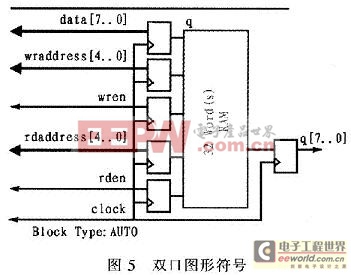

雙口RAM分為真、假2種雙口。真雙口2個端口都可以讀寫,互不干擾。本次設計根據實際需要,添加的RAM模塊一端只讀,另一端只寫,讀寫互不干擾。根據上述分析可知,開關控制信號只能知道有開關控制動作發生,但是不能識別具體哪個開關發生了動作。因此,設計中首先利用MegaWizardPlug_In Manager中的宏功能塊RAM:2_PORT產生1個雙口RAM存儲塊,然后對這個宏功能模塊的參數進行適當調整,產生一個滿足自己特定要求的模塊,如圖5所示。

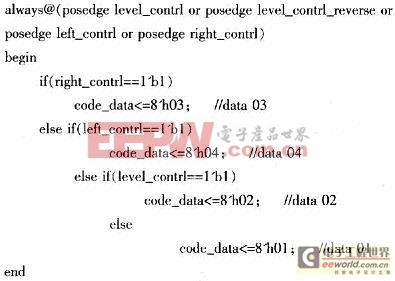

設計過程中,首先將開關動作進行編碼。然后將編碼后的數據存進空間大小為8的雙口RAM中。當BF561檢測到PF9上的脈沖后,在PF中斷中讀取RAM中指定地址的數據,然后根據這個數據進行開關狀態解碼并按解碼后的控制信息對2塊MAX4312器件進行操作以控制視頻通道。對開關動作進行的編碼程序代碼如下:

整個設計有4種開關動作,程序中分別將其編碼成數據0l、02、03、04,然后將編碼后的這4個數據存入雙口模塊中,等待BF561來讀取并進行解碼。圖6是SignalTapⅡLogic Analyzer中對脈沖開關向右撥動后存入RAM中的數據進行采樣。

程序中RAM的讀信號rden_signal是由DSP發送的地址信號DSP_A、BANK選擇信號DSP_AMSl以及DSP讀信號DSP_ARE進行控制的。當DSP不從雙口讀取數據時,必須給DSP的數據線賦值高阻,以免影響SDRAM對DSP數據線的操作。賦值指令如下:assignDSP_D=(rden_signal=l 'b1)?DSP_D_TEMP;8 'hzz;其中DSP_D_TEMP是從雙口中讀取的數據。

3 結論

首先介紹了整個系統的工業背景和硬件架構,然后著重闡述了怎樣在FPGA中處理開關控制信號,以達到可靠響應每個開關動作的目的。整個設計程序是在QuartusⅡ平臺上用Verilog硬件描述語言編寫,利用QuartusⅡ中的下載工具和SignalTapⅡLogic Analyzer工具進行下載、實時采樣,并多次調試驗證。本次設計已經成功應用于布機告警系統中,每次撥動開關都能準確、可靠的切換視頻通道。雖然此系統中只有兩種開關,但是整個程序的設計思想對多種開關控制也是通用的,只需在細節上稍作改變就能識別多種開關動作。

評論