一種基于EP2SGX系列FPGA的PCI接口設計

3 PCI接口設計實現

本設計利用ALTERA公司的QuartusIl7.2軟件和硬件描述語言,采用自頂向下的設計方法進行PCI接口的邏輯設計,并利用QuartusII軟件對設計進行了功能和時序仿真。

設計的具體流程如下:首先從總體上考慮:PCI接口作為一個功能模塊,嵌入在FPGA內部,內側面向用戶邏輯,外側通過芯片的I/O管腳與PCI總線相連。在用戶端,需要把復雜的PCI總線命令轉換為便于用戶使用的類似ISA總線的命令格式,把地址線與數據線分離,并產生單獨的讀寫控制信號。其次,根據總體要求,進行頂層設計和內部模塊劃分。最后,對具體的功能模塊用軟件編程實現并進行功能仿真。

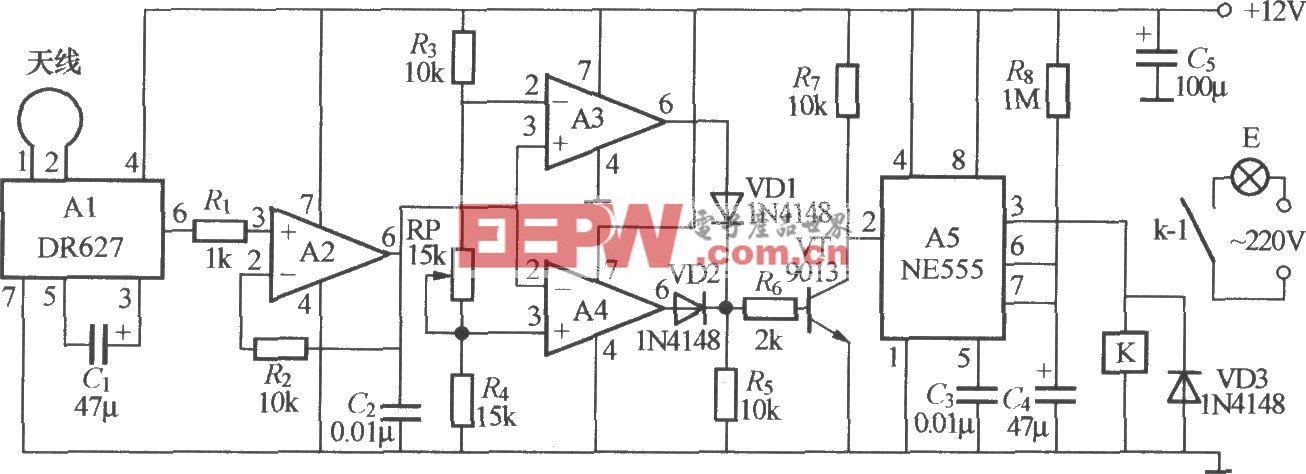

本設計中PCI接口的總體框圖如圖4所示。由圖4可知,PCI接口主要由地址/命令鎖存和譯碼、內部通信、外部通信和總線狀態機、中斷處理等模塊組成。

3.1 地址/命令鎖存和譯碼

由于PCI總線為地址和數據復用型總線,在使用中需將地址和數據進行分離,首先要對PCI總線上的32位地址/數據總線鎖存。譯碼是對來自主機的PCI總線命令信號CBE[3..0]和IDSEL信號進行識別,并相應地向內部邏輯發出配置空間讀寫操作、I/O讀寫操作、存儲器讀寫操作等信號。

3.2 外部通信

外部通信接口主要完成對PCI總線的應答,并發出相應的信號。對于瀆寫操作,接口發出DEVSEL#信號響應PCI的FRAME#信號,完成握手。PCI協議規定了在交易期間對地址/數據總線和命令/字節使能總線進行奇偶校驗。讀交易期間,接口被要求驅動PAR信號線;寫交易期間,目標將計算AD[31..0]和CBE[3..0]上的奇偶性,并把PERR信號送給PCI。

3.3 內部通信

內部通信接口主要產,豐面向用戶端,便于用戶使用的一信號,包括復位信號、分離的讀和寫信號、地址總線、32位的數據讀寫總線。

3.4 總線狀態機

該模塊足本設計的關鍵部分,其主要功能是根據PCI協議產生總時序來控制總線交易。總線狀態機包含的狀態主要有總線空閑狀態、總線停靠狀態、主設備數據傳輸狀態、從設備數據傳輸狀態、配置空間讀寫狀態、目標I/O空間讀寫狀態、主設備讀寫狀態、總線翻轉狀態、數據傳輸終止狀態等。以上各狀態主要依據輸入的PCIRST、FRAME#、IDSEL、CBE [3..0 ]、GNT#、IRDY#、TRDY#、STOP#等信號變化進行狀態轉換。

3.5 中斷處理

本模塊主要實現各種外部中斷源的輸入處理、中斷允許寄存器和中斷狀態寄存器的控制和管理、INTA#信號的輸出處理等。

評論