3 主要模塊軟件程序

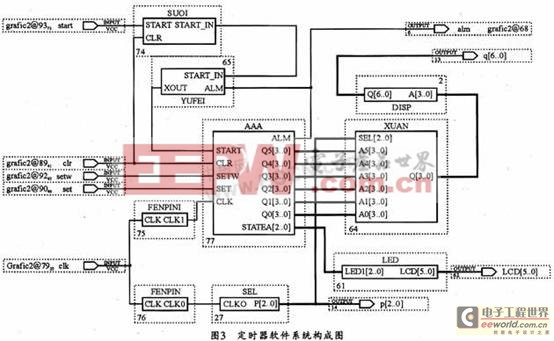

圖3所示是該定時器的軟件系統構成。本軟件包括控制/定時模塊和顯示模塊兩大部分。

3.1 控制/定時模塊

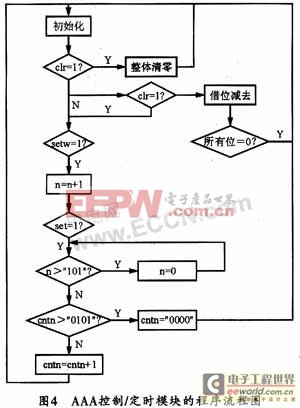

AAA控制/定時模塊是該定時器的核心部分,該模塊的程序流程圖如圖4所示。

當START為高電平時,該定時器將進入倒計時階段。當CLK脈沖上升沿到來時,計數以秒的速度減1,直到計時結束,使ALM位為高電平為止。CLR為復位端,可用來清零,通常采用異步復位方式。SETW用于選位,高電平有效。SET用于對選定的位進行置數,也是高電平有效。ALM輸出端將在定時結束時產生高電平。Q0~Q5為四位BCD碼輸出端口,主要用于顯示。

評論