增量型光電編碼器抗抖動二倍頻電路的設計

2.2.2 FPGA濾除編碼器抖動及仿真結果

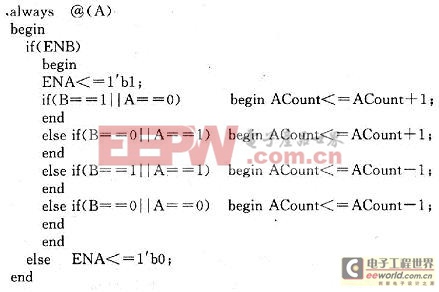

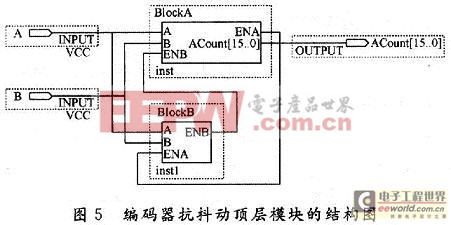

根據以上分析,本文采用FPGA濾除增量型光電編碼器輸出抖動脈沖。編譯環境采用QuartusⅡ8.O。在FPGA中使用圖形和語言結合的方法設計邏輯模塊。內部的邏輯子模塊采用Verilog語言來實現。頂層模塊的結構圖如圖5所示。A和B輸入引腳連接增量型編碼器A相和B相信號。Acount為16位的數據寄存器,輸出當前編碼器的位置。頂層設計中包含兩個模塊,一個是根據編碼器的B相跳變沿記錄來濾除編碼器A相抖動脈沖的BlockA模塊,該模塊根據濾除后的A相脈沖數據個數并記錄脈沖數據。Verilog的主要程序如下:

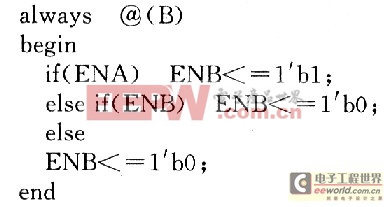

另一個模塊BlockB主要完成的功能是濾除編碼器B相的抖動脈沖。根據分析濾除編碼器抖動的原理,ENA引腳為BlockA模塊的輸出引腳,當A相輸入引腳有跳變時ENA為1,A相引腳有連續的跳變或者接下來B相有跳變時ENA為0。ENB為編碼器B相跳變使能引腳,當ENA為1時如果B相有跳變ENB為1,當ENA為1時如果B相有連續跳變ENB為0。主要程序如下:

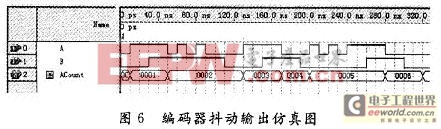

以圖4(a)的編碼器抖動輸出仿真為例,仿真效果如圖6所示。從圖中分析,A相輸出7個脈沖,應該輸出3個脈沖,二倍頻后是14個脈沖,應該輸出6個脈沖,經過濾除后脈沖計數器數為6個。A相的抖動脈沖得到有效的濾除。

3 結語

現場調試結果證明,該算法可以消除工業現場出現的干擾和抖動現象,能夠準確地記錄脈沖數據。此濾波方法可以采用軟件濾波,但是軟件濾波需要的引腳較多,采用兩個中斷引腳響應A相的上升沿和下降沿,浪費CPU資源。采用FPGA實現編碼器的濾波,設計方便,改動靈活。

評論