基于PM3388和FPGA的網絡接口的研究設計

3 硬件設計與實現

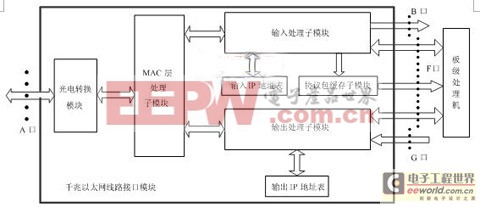

經過對十接口千兆以太網線路接口卡功能和性能需求進行認真分析,按照功能清晰、接口簡單、實現容易的原則,設計了其實現方案,并按照設計方案對千兆以太網線路接口卡進行了子模塊劃分,共分為光電轉換子模塊、MAC層處理子模塊、輸入處理子模塊、輸出處理子模塊、輸入IP地址表子模塊、輸出IP地址表子模塊和協議報文緩存子模塊等七個子模塊。千兆線路接口卡各子模塊和外部接口關系如圖2所示。

圖 2 十接口千兆以太網線路接口卡模塊結構圖

其中MAC層處理子模塊是千兆線路接口卡設計的核心,選用PMC-Sierra公司的PM3388芯片為MAC層處理芯片, PM3388芯片是目前市場上唯一支持十接口的千兆以太網控制器,其功能特性如下:

- 十路千兆以太網控制器(同時完成PHY層和MAC層功能);

- 通過內部十個SERDES接口直接與光電轉換模塊相連。每個SERDES接口兼容IEEE 802.3-2000 PMA(Physical Medium Attachment)物理層規范;

- 從網絡上接收8B/10B格式碼流,完成數據及時鐘恢復;

- 每個接口提供多播地址過濾及8個單播地址過濾;

- 提供標準的IEEE 802.3 以太網幀格式完整性檢驗,并具有過濾功能;

- 內部提供224K字節接收FIFO和64K發送FIFO,可在十路接口上靈活配置;

- 提供SATURN標準的PL4(POS-PHY Level 4)標準16位LVDS總線接口,速率可達700Mbps;

- 提供標準IEEE 1149.1 JTAG測試端口;

- 提供微處理器接口;

- 提供線路側環回和系統側環回的系統級調試功能;

- 提供豐富的配置及統計寄存器。

PM3388工作流程包括接收處理和發送處理兩部分。1.接收通路:PM3388從光電轉換子模塊接收串行差分電信號,經過串/并轉換、8B/10B解碼后,進行以太網幀完整性檢驗和地址過濾,

為了保證PL4接口達到十路1Gbps的速率,PM3388的參考時鐘引腳接160MHz時鐘晶振,輸入輸出接口的采樣時鐘通過將該時鐘倍頻獲得320MHz時鐘,輸入輸出數據分別在時鐘雙沿采樣,可以獲得640Mbps的數據數率,總帶寬達10.24Gbps,可以滿足0丟包率性能對帶寬的要求。

此外,輸入處理FPGA是千兆以太網線路接口卡模塊設計的重點之一,主要的功能是將各種標準的MAC幀數據格式轉換為網絡層統一的數據格式,為網絡層處理屏蔽掉底層物理接口。

輸入處理FPGA采用Altera公司Stratix GX系列的EP1SGX25F芯片,該芯片具有25660個邏輯單元,16個高速收發器通道,39個源同步IO和總數為1944576比特的RAM,可以滿足實現輸出處理功能對資源的要求。

輸入處理子模塊主要完成輸入處理和配置統計兩大功能:第一、接收MAC層處理子模塊發送過來的數據片,完成MAC幀重組和十路數據合路處理,再根據MAC幀封裝的三層協議類型實現數據包的分類處理,按照不同的處理要求把數據包分別送B接口、F接口或者同時送兩個接口。送往B口的數據包經過MAC幀格式拆封和B口格式封裝后輸出到轉發模塊,送往F口的數據經過數據寬度和時鐘頻率的變換后輸出到協議FIFO。第二、線路接口卡上電初始化時,輸入FPGA通過板級處理機獲取本線路接口卡所在的機架號和端口號等信息,并把這些信息插入到送往轉發處理模塊的數據包的B口格式字中。輸入處理FPGA還要實現大量的統計功能,統計項包括每個接口接收到的總幀數、錯誤幀數、丟棄幀數、IPv4單組播包數、IPv6單組播包數、MPLS單播包數、送往B口包數和送往協議FIFO包數等,并根據命令把統計信息送往板級處理機。

合成孔徑雷達相關文章:合成孔徑雷達原理

評論