基于FPGA的快速9/7整形離散小波變換系統

2 9/7二維離散小波變換的系統設計過程

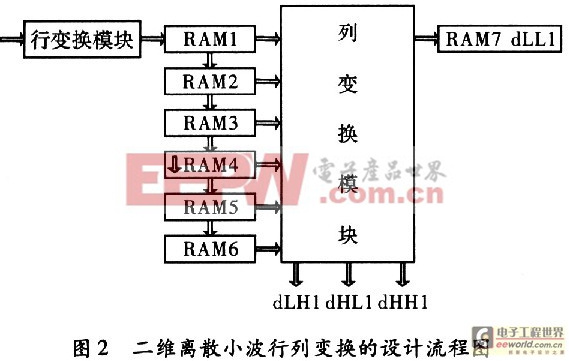

本文在Xilinx公司提供的ISE7.1集成設計軟件環境下,采用VHDL語言設計實現9/7二維離散小波變換系統,首先進行小波行變換,行變換后的數據按照行數輸入內部RAM緩存,然后對行變換后的數據再進行列變換,最后將低頻系數dLLl輸入RAM緩存,其余高頻系數dLHl,dHLl,dHHl輸出到外掛RAM中緩存,系統設計流程,如圖2所示。

2.1 行變換過程

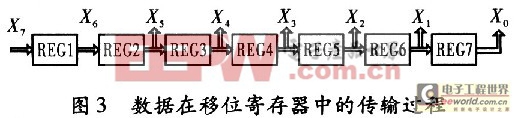

首先,使用7個移位寄存器來實現對數據的讀寫傳輸,每到來一個時鐘控制信號(clk),就往移位寄存器中讀寫一個數據,數據在移位寄存器中的傳輸過程,如圖3所示。

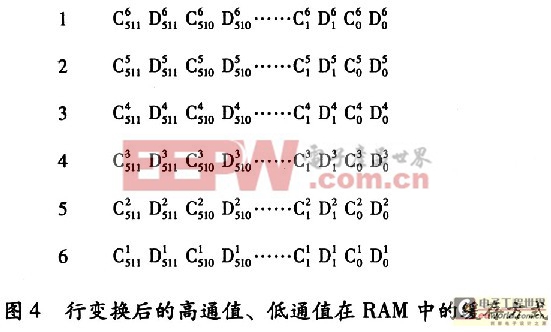

當輸入第5個數據時,就可以根據式(1)和式(5)分別計算出第一個高通系數值D0和第一個低通系數值C0,下一個時鐘控制信號讀入第6個數據時,不進行操作,當控制讀入第7個數據時,根據式(2)和式(6)分別計算出第2個高通系數值Dj和第2個低通系數值Cj,小波行變換后的高通系數D和低通系數C采用地址傳輸的方式交叉存儲到6個內部RAM當中,如圖4所示。

評論