基于CPLD的壓電生物傳感器檢測電路設計

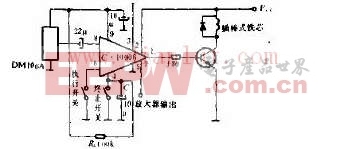

圖1中,USB口為壓電生物傳感器與檢測電路相連接的接口;RS-232口為與計算機相連接的接口,將數字化的傳感器信號(頻率值)上傳到計算機,由計算機(PC機)實現傳感器信號的實時采集和顯示,采集數據程序由VC++6。0編寫;OSC1為提供系統工作時鐘振蕩電路,由TTL芯片和12MHz標準晶振組成,產生1s脈沖信號,作為CPLD工作時鐘輸入、RS-232通信時序脈沖以及數碼管動態顯示時序脈沖,準確度高、且精確;OSC2為傳感器振蕩電路,經過幾代反復改良,在氣相、液相均能夠正常振蕩且波形正常,將傳感器表面生物反應信號轉化成脈沖信號,輸入CPLD進行信號數據采集;數碼顯示采用共陰極8×8段數碼管,動態掃描顯示當前傳感器信號值和簡單數據分析判斷結果;電源給系統提供直流5V工作電壓,含有直流6~15V變成5V穩壓電路;RS-232電平轉換電路將從CPLD輸出的CMOS電平轉化為計算機所接受的TTL電平,而且可增加數據傳輸距離。

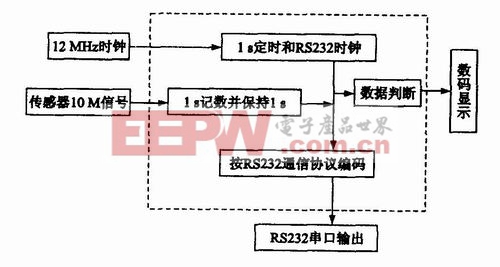

作為系統內核的CPLD,采用Verilog HDL硬件設計語言、MAX+plusII10。1編譯系統編寫基于Altera公司CPLD(MAX7128)器件的內核程序,設計實現了秒時鐘定時、10MHz頻率測量、RS-232通信時序發生器、RS-232協議數據通信、頻率數據判斷簡單分析以及數碼管動態掃描顯示控制等綜合功能,其原理如圖2所示。

圖2 CPLD內核原理圖

評論