FPGA高速硬件在環(huán)仿真器實(shí)現(xiàn)電機(jī)控制器測試

電機(jī)控制器將參考波形與三角載波相比較,從而確定門控制信號(hào)的狀態(tài)。

當(dāng) 時(shí),上面一個(gè)電力電子器件的門極控制信號(hào)為高, 下面的器件的控制信號(hào)為低

時(shí),上面一個(gè)電力電子器件的門極控制信號(hào)為高, 下面的器件的控制信號(hào)為低

當(dāng) 時(shí),上面一個(gè)電力電子器件的門極控制信號(hào)為低, 下面的器件的控制信號(hào)為高

時(shí),上面一個(gè)電力電子器件的門極控制信號(hào)為低, 下面的器件的控制信號(hào)為高

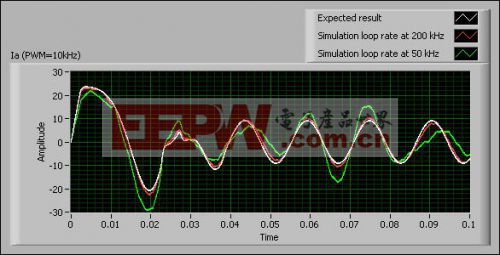

準(zhǔn)確檢測門信號(hào)的開關(guān)時(shí)刻對(duì)仿真器正確產(chǎn)生仿真信號(hào)來說非常重要。否則仿真器可能產(chǎn)生抖動(dòng)、非特征諧波等不準(zhǔn)確結(jié)果,甚至變得不穩(wěn)定。下圖為PMSM電機(jī)驅(qū)動(dòng)的電流波形仿真結(jié)果。

PWM頻率為10 kHz。可以看到,50 kHz的仿真循環(huán)速率還不足以讓仿真器及時(shí)地檢測出開關(guān)時(shí)刻

因此不能獲得精確結(jié)果。檢測結(jié)果中包含了不想要的諧波分量,使結(jié)果與期望值偏差很大。而在200 kHz的循環(huán)速率下,檢測結(jié)果就好了很多。

為了獲得精確結(jié)果,仿真器的采樣間隔必須比控制器的PWM周期小很多。如此高循環(huán)速率的應(yīng)用使基于FPGA的方案成為理想選擇。我們的定點(diǎn)PMSM模型及定點(diǎn)BLDC模型均能在40個(gè)FPGA時(shí)鐘周期內(nèi)完成一次更新運(yùn)算。

提示:有時(shí),期望仿真循環(huán)速率可能超過模擬了I/O所能夠達(dá)到的速率。一般此時(shí)無需更新模擬I/O(扭矩輸入、電流輸出等)來匹配仿真循環(huán)率,用戶可使用多頻編程來保持?jǐn)?shù)字I/O及仿真循環(huán)處于高速率,從而用于門信號(hào)開關(guān)時(shí)刻的精確檢測,而將模擬I/O設(shè)置于另一個(gè)循環(huán)狀態(tài),之后再通過FIFO在兩個(gè)不同頻率的循環(huán)間傳輸數(shù)據(jù)。

設(shè)計(jì)的前提假設(shè)

a. 電力電子器件的理想開關(guān)模型

將電力電子器件建模為理想開關(guān),當(dāng)門信號(hào)為真(高)時(shí),開關(guān)為理想的短路電路。當(dāng)門信號(hào)為假(低)時(shí),開關(guān)為理想的開路電路。理想開關(guān)模型非常適用于系統(tǒng)級(jí)仿真,此時(shí)我們不關(guān)心電力電子器件的寄生效應(yīng)。此外,理想開關(guān)模型可大幅提升仿真速度。

對(duì)于電力電子器件的熱損失,可以計(jì)算其等效電阻,并將此電阻值計(jì)入電機(jī)的總電阻。

b. 積分方法

電機(jī)的數(shù)學(xué)模型是一組微分方程。當(dāng)在FPGA上仿真電機(jī)驅(qū)動(dòng)模型時(shí),實(shí)際上是在FPGA上對(duì)這些微分方程進(jìn)行積分。由于期望的積分步長非常的小,僅為幾微秒的量級(jí)。

所以用戶可選擇最簡單的積分方法,如歐拉方法,此方法適用于小步長情況。

評(píng)論