基于Xilinx FPGA的千兆以太網控制器的開發

1)發送引擎

發送引擎通過客戶發送端口接收以太網的數據幀,并在幀頭添加幀引導區域,甚至在幀長小于最短要求時,添加一定的冗余比特。同時,該模塊還會在連續的數據幀之間插入以太網協議所規定的最小延時,將用戶數據轉化成標準的GMII數據幀,并送至GMII模塊。在應用時,面向用戶的操作就是將用戶數據讀入GEMAC核內部

該模塊接口信號的簡要信息如表10-10所列。

表10-10 發送引擎接口信號列表

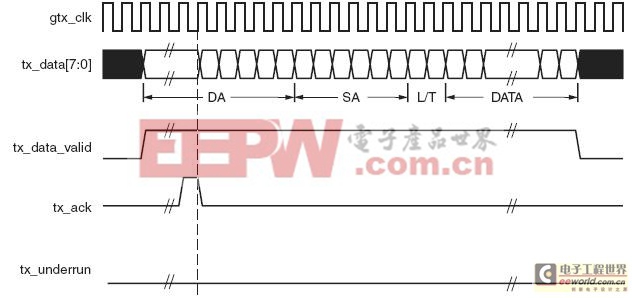

發送引擎的時序如圖10-38所示。當客戶端有數據發送時,將tx_data_valid拉高,同時將數據的第一個字節置于tx_data端口;當GEMAC將第一字節數據讀入后,會將tx_ack信號拉高,用戶端邏輯檢測到tx_ack為高時,要在下一個時鐘上升沿將其余的數據發送到數據端口上,當數據發送完畢后,將x_data_valid拉低。

圖10-38 發送引擎的時序圖

2)接收引擎

接收引擎接收來自GMII模塊的數據,去掉幀頭的引導區域,包括為了增加幀長的冗余比特。此外,該模塊還能根據數據幀中的檢驗序列區域、接收到的GMII錯誤碼字以及幀長信息完成錯誤檢測,主要接口信號的簡要說明如表10-11所列。

表10-11 接收引擎接口信號列表

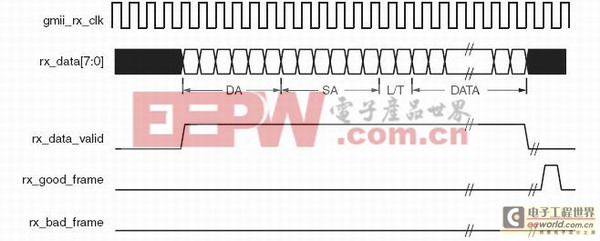

接收引擎的時序如圖10-39所示。客戶端邏輯必須在任何時候都準備好接收數據,因為在GEMAC核中沒有接收緩存,有時延就會丟失數據,因此用戶可自己添加緩沖邏輯。rx_data_valid為高時立即開始接收連續數據,在檢測到rx_data_valid變低后,判斷rx_good_frame信號的電平,如果為高則繼續處理該幀數據,否則直接丟棄。

圖10-39 接收引擎的時序圖

評論