基于Xilinx FPGA的千兆以太網控制器的開發

2)MAC接收模塊

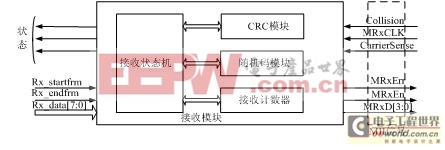

MAC接收模塊結構如圖10-33所示,負責數據幀的接收。當外部PHY將通信信道的串行數據轉換為半字節長的并行數據并發送給接收模塊后,接收模塊會將這些半字節數據轉換為字節數據,然后經過地址識別、CRC校驗、長度判斷等操作后,再通過主機接口寫入外部存儲器,并在主機接口模塊的接收隊列中記錄幀的相關信息。此外,接收模塊還負責前序碼和CRC的移除。

圖10-33 以太網MAC接收模塊的結構示意圖

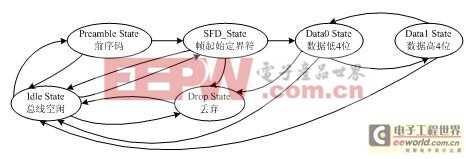

接收過程的接收狀態機由Idle_State、Drop_State、Preamble_State、SFD_State、Data0_State、Data1_State等六個狀態組成, 其狀態轉移圖如圖10-34所示。

圖10-34 接收狀態機的狀態轉移圖

當接收模塊檢測到數據有效信號之后,,狀態機將進入Preamble_State,并開始接收前序碼。此后狀態機進入SFD_State,接收一個字節的幀起始定界符,之后根據IFGcnt計數器的值進入不同的狀態。如果IFGcnt所確定的時間大于96個比特時間,狀態機將進入Data0狀態以接收字節的低4位,然后是Data1狀態,并接收字節的高4位,之后又回到Data0狀態。狀態機就一直在這兩個狀態之間循環,直到數據接收完畢(PHY清除MRxDV信號)后進入Idle,以重新等待接收新的數據;如果接收到幀起始定界符時,IFGcnt計數器所確定的時間小于96個比特時間,那么狀態機將進入Drop_State狀態,并一直維持該狀態直到數據有效信號結束(PHY清除MRxDV信號)。之后,狀態機再回到Idle等待接收新的數據。如果在接收前序碼、幀起始定界符和數據期間,數據有效信號被清除,那么狀態機將回到Idle。

3)MII管理模塊

MII管理模塊用于控制MAC與外部PHY之間的接口,用于對PHY進行配置并讀取其狀態信息。該接口由時鐘信號MDC和雙向數據信號MDIO組成。MII管理模塊則由時鐘生成模塊、移位寄存器模塊和輸出控制模塊三部分組成。

時鐘生成模塊可以根據系統時鐘和系統設置中的分頻系數來產生MII 管理模塊的時鐘信號MDC(10 Mbps速率時為2.5 MHz, 100 Mbps速率時為25 MHz)。移位寄存器模塊既可用于對PHY的控制數據進行寫入操作,也可用于對PHY的狀態信息進行讀出操作。寫控制數據時,移位寄存器根據其他模塊的控制信號將并行控制數據轉換為串行數據;而在讀狀態信息時,移位寄存器則將PHY的串行數據轉換為并行數據,MAC中的其他模塊可將該并行數據寫入適當的寄存器。

由于MDIO是雙向信號,因此輸出控制模塊就用來決定MDIO是處于輸入狀態還是輸出狀態。當MDIO處于輸出狀態時,移位寄存器輸出的串行控制數據在經過時鐘同步后發送到PHY;當MDIO處于輸入狀態時,移位寄存器將數據線上的串行數據轉換為并行數據

4)主機接口模塊

主機接口是運行以太網的上層協議(如TCP/IP協議)與MAC控制器的接口。通過該接口,上層協議可以設置MAC的工作模式并讀取MAC的狀態信息。該接口還可用于上層協議與MAC之間的數據交換。

主機接口模塊內有一組寄存器,可用于存儲上層協議對MAC設置的參數以及MAC的狀態信息。上層協議對MAC設置的參數包括接收超短幀的使能、添加填充碼使能、發送超長幀的使能、添加CRC校驗值使能、全雙工模式或半雙工模式、持超長延遲使能、混雜模式(Promiscuous)、接收廣播幀使能、發送和接收使能、中斷源和中斷使能、幀間間隙的長度、最大幀和最小幀的長度、重試限制和沖突時間窗、MII地址和MII控制命令、接收和發送隊列的長度以及本機MAC地址等。

上層協議通過MAC發送和接收數據的操作主要由主機接口模塊內的兩個隊列來進行管理,這兩個隊列用于對等待發送的多個幀和接收到的多個幀進行排隊。發送隊列主要記錄等待發送的幀的相關信息、發送該幀時對MAC的設置以及該幀發送完之后產生的狀態信息。幀的相關信息包括幀的長度、幀在外部存儲器中的地址、該幀是否準備好發送以及隊列中是否還有其它幀等待發送;對MAC的設置則包括中斷使能、填充使能、CRC使能;產生的狀態信息包括成功發送之前的重試次數、由于達到重試限制而放棄發送、發送時產生的滯后沖突以及成功發送之前發生過的延遲。

接收隊列主要對接收到的數據幀進行排隊并記錄每個接收到的幀信息。這些信息包括幀的長度、是控制幀還是普通數據幀、幀中包含無效符號、接收到的幀太長或太短、發生CRC錯誤、接收的過程中發生滯后沖突、幀是否接收完、隊列中是否還有其它已接收到的幀以及幀存儲在外部存儲器中的地址等。同時隊列中還有針對每個幀的設置位,用來設置是否在接收到幀時產生中斷。發送隊列和接收隊列的長度都可以在控制寄存器中進行設置。

評論