一種基于FPGA的電子穩像系統的研究與設計

1 系統涉及的關鍵技術

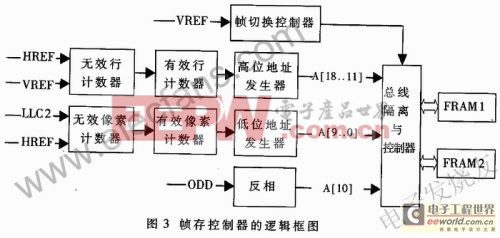

攝像頭輸入的PAL制式電視信號首先通過視頻處理接口完成對其解碼、同步和數字化的工作,數字化后的圖像信息進入到由FPGA實現的幀存控制器中,完成數據的交換(數據的緩沖),同時完成系統要求的去隔行和放大的操作,最后處理好的數據通過VGA控制器,完成時序變化,經視頻、A變為模擬信號送到VGA監視器上實時顯示。

1.1 視頻處理接口

由于在進行視頻處理時,多為從攝像頭輸入模擬信號,如NTSC或PAL制式電視信號,除圖像信號外,還包括行同步信號、行消隱信號、場同步信號、場消隱信號以及槽脈沖信號等。因而對視頻信號進行A/D轉換的電路也非常復雜。Philips公司將這些轉換電路集成到了一塊芯片中,從而生產出功能強大的視頻輸入處理芯片SAA7111,為視頻信號的數字化應用提供了極大的方便。

系統設計采用SAA7111對復合信號進行采樣、同步產生、亮色分離并輸出標準的數字化信號。SAA7111輸出的數字化圖像信息符合CCIR.601建議,PAL制式的模擬信號數字化后的圖像分辨率為720×572,像素時鐘13.5MHz。在本穩像系統中要求圖像輸出符合VGA(640×480,60Hz)標準,因此在采集數據時要對數據進行選擇,避開行、場消隱信號和部分有效像素信息,在較大的圖像中截取所需要的大小。SAA7111向幀存控制電路輸出像素時鐘(LCC2)、水平參數(HREF)、垂直參考(VREF)、奇偶場標志信號(ODD)和16位像素信息(RGB565).其中LCC2用來同步整個采集系統;HREF高電平有效,對應一行720個有效像素;VREF高電平有效,對應一場信號中的286個有效行;ODD=1時,標志當前場為奇數場;ODD=0時,標志當前場為偶數場。采用16位RGB表示每個像素的彩色信息。圖1(a)為數字化圖像中的一行像素的時序圖。其中兩個HREF分別表示有效行的起始與結束位置,實際為一個信號;可以清楚地看到一行中有效的720個像素與像素時鐘LLC2的對應關系,在采集時通過幀存器控制電路選擇其中部的640個像素進行采集。圖1(b)為一幀數字圖像的輸出時序圖。可以看到在第624~22行時,VREF處于無效狀態,因此在后續的采集中,這部分的信息不予處理并通過ODD的電平區分奇偶場數據。

p2p機相關文章:p2p原理

評論