一種基于FPGA的語(yǔ)音錄制與回放系統(tǒng)的設(shè)計(jì)

1.1芯片工作原理

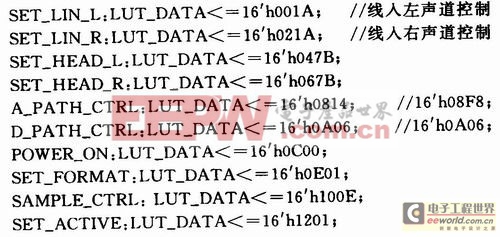

音頻編/解碼芯片WM8731上電后必須將工作模式設(shè)置在系統(tǒng)要求的狀態(tài)下,因此上電后需要用VERILOGHDL編寫程序模塊對(duì)芯片的工作模式進(jìn)行設(shè)置。該語(yǔ)音編/解碼芯片有多種工作模式,A/D變換后,語(yǔ)音的采樣頻率與采樣位寬都需要根據(jù)系統(tǒng)的具體要求,合理配置。語(yǔ)音芯片的配置時(shí)序?yàn)镮2C模式,芯片接口為主模式,即由WM8731提供位時(shí)鐘,A/D轉(zhuǎn)換和D/A轉(zhuǎn)換的左、右聲道控制相位時(shí)鐘,以及轉(zhuǎn)換后的數(shù)據(jù)PCM碼輸送給FPGA處理器。以下為芯片配置字列表,WM8731內(nèi)部控制字寄存器有16個(gè),在芯片初始化時(shí),在制作ROM表格中完成。相應(yīng)的程序設(shè)置如下:

1.2配置單元模塊

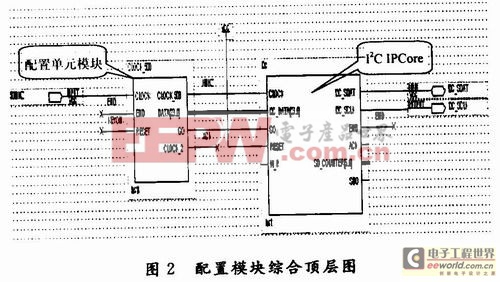

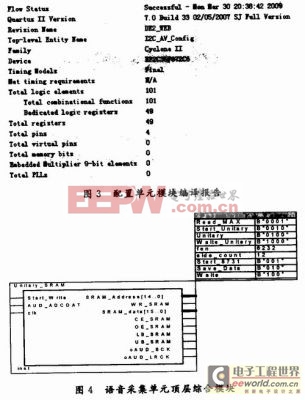

配置單元模塊綜合頂層圖如圖2所示。從程序編譯分析報(bào)告(見(jiàn)圖3)可以得出,該單元模塊消耗了101個(gè)邏輯單元,它作為語(yǔ)音采集模塊的一個(gè)子模塊。在配置電路中,模塊CLOCK_50將輸入的50MHz系統(tǒng)時(shí)鐘分頻為1MHz,作為I2C總線模塊的工作時(shí)鐘,CLOCK_50模塊中寫出的上面程序代碼是一個(gè)表格,存儲(chǔ)了配置的控制字。I2C總線模塊的I2C_SDAT和I2C_SCLK是數(shù)據(jù)線和時(shí)鐘線,DE2板固定分配了專門的I2C數(shù)據(jù)線和時(shí)鐘線的引腳線。

評(píng)論