一種基于FPGA的語音錄制與回放系統的設計

0引言

隨著微電子技術的發展,系統集成向高速、高集成度、低功耗發展已經成為必然,同時SoPC技術也應用而生。SoPC將軟硬件集成于單個可編程邏輯器件平臺,使得系統設計更加簡潔靈活。SoPC綜合了SoC,PLD和FPGA的優點,集成了硬核和軟核CPU、OSP、存儲器、外圍I/O及可編程邏輯,用戶可以利用SoPC平臺自行設計高速、高性能的CPU和DSP處理器,使得電子系統設計進入一個嶄新的模式。

該設計運用SoPC技術實現嵌入式數字化語音錄制與回放。其中,介紹了在FPGA上構建WM8731的I2C總線,以及數字化語音在SRAM中的存儲,并利用Matlab7.0.4軟件對所采集的語音數據進行仿真。SoPC是現在電子技術、電子系統設計的匯聚點和發展方向。充分體現了其高性能、設計靈活和易用等特點。

1系統整體方案

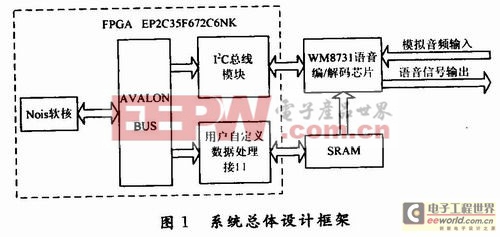

系統以Altera公司的FPGA芯片(CycloneⅡ系列)EP2C35F672C6NK為平臺,結合音頻編/解碼芯片WM8731實現語音錄制與回放。該FPGA芯片具有豐富的片內資源,大量的邏輯宏單元和多個硬件乘法器,大量的自定義I/O接口,此外還有4個鎖相環,為系統提供實時時鐘。設計中充分利用了FPGA的高速并行和Avalon總線自定義硬件外設的優勢,從而構建了一個高集成度、高性能的系統。

語音通過話筒輸入,由音頻編/解碼芯片WM8731以8kHz的A/D采樣率轉換成16位PCM碼緩存。此外,為確保采集的語音數據不丟失,先將語音存儲在SRAM中,再作后續處理。整體系統框架圖1所示。

評論