基于FPGA的DDFS與DDWS兩種實現方式

2 數字實現

2.1 DDFS的數字實現

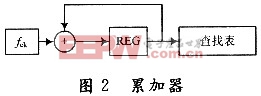

由于D/A之前都是數字部分,為了分析其原理數字控制的實現過程,參考如圖2所示結構。

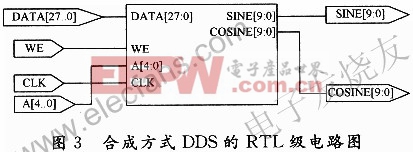

相位累加器是由一個加法器和一個寄存器構成,假設累加器位數N=6,那么000000代表0弧度,000001代表弧度,相應的000010代表(2π/64)*2弧度,111111代表(2π/64)*63弧度。若頻率控制字FCW=000011,并且累加器中的初始相位為O,則經過N=21個時鐘周期后形成的二進制序列為000000,000011,…,111111,對應的相位分別為O,(2π/64)*3,…,(2π/64)*63。當第22個時鐘周期到來時,加法器溢出,所有位數重置為0,另一個循環周期開始。查找表可以用FPGA中BlockRAM做成,前面的二進制序列作為地址,相位對應的幅度值作為地址對應的值存儲起來,這樣在時鐘頻率的控制下通過二進制序列可從BlockRAM中讀取相應的幅值,經過D/A后就為所需要的模擬波形。圖3為FPGA綜合后的RTL級電路圖。

2.2 DDWS的數字買現

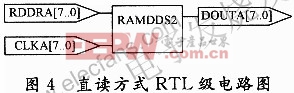

DDWS的數字實現較為簡單,把通過Matlab抽樣量化后的數據直接保存為.BAT數據格式,然后在FPGA中用IP核的BlockRAM生成一個ROM,把數據存儲進去,這樣就可以根據時鐘要求輸出需要的數據了。

圖4為FPGA仿真后的RTL級電路圖。

評論