應用EDA仿真技術解決FPGA設計開發中故障的方法

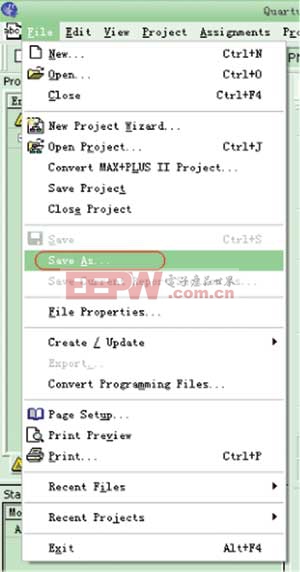

將list file另存為文本格式文件即可,如圖4所示。

圖4 “另存為”選項界面

此后可以把這個文本文件中無用的描述刪掉,只留SignalTap抓出來的數據(空格、h等符號也要刪掉),另存為.dat文件供仿真使用。

有了故障出現時的輸入數據,我們就可以在仿真環境下構建故障出現的條件。

②利用.dat文件建立bug出現的條件

用verilog語言編寫仿真文件(testbench),使用語句$readmemh或$readmemb將.dat文件中的數據存儲到一個設定的ram中,如:$readmemh(“s.dat”,ram)。

注意$readmemh讀取是按照十六進制數據進行(認為.dat文件中的數據都是十六進制數),會自動將其轉換為4位二進制數存入ram中,所以設定的ram位寬要是.dat文件中數據位寬的4倍;使用$readmemb時,存儲SignalTap所抓信號時,信號都要先設定為binary類型,ram位寬就是.dat文件數據的位寬。ram的深度為.dat文件中數據的個數。

然后在程序里把ram中數據按照所對應時鐘沿輸出到一個寄存器變量中,ram地址累加即可。

always@(posedge clk)

begin

data=ram[addr];

addr=addr+1'b1;

end

復現bug存在條件時,需將模塊的輸入信號與ram中的數據位相對應,仿真文件調用模塊時,將寄存器data對應位作為輸入接入即可。

評論