一種基于FPGA的信道化接收機的研究與設計

4 測試結果

系統輸入測試信號為單頻正弦信號,VPP為1 V,信號經過AD采樣,DDC,信道化后,數據結果經過PCI上傳給PC機作分析和顯示。

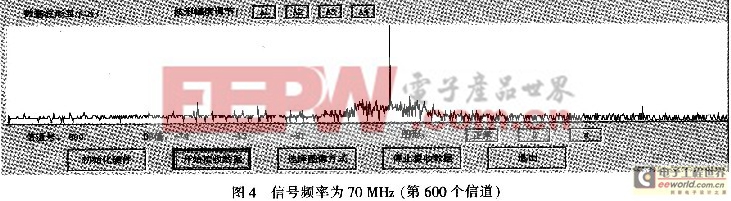

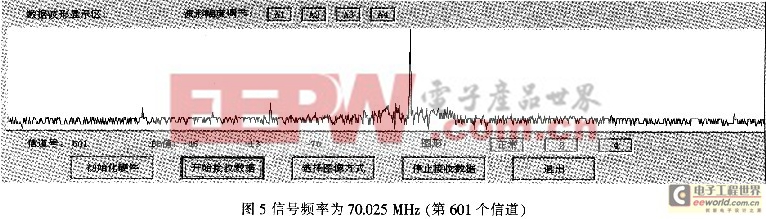

用Microsoft Visual C++6.0制作的界面中:橫坐標是信道號,縱坐標是歸一化功率值(dB),以數據形式顯示的內容有:信號功率最大值對應的信道號、子信道輸出相對于輸入幅度的dB值以及相鄰的兩個信道的dB值。如圖4和圖5所示,輸入信號頻率分別為70 MHz,70.025 MHz,經過信道化后,在對應的信道號上都能輸出譜線,頻率分辨率達到25 kHz。經過多次重復測試,系統對相鄰信道的帶外抑制都達到55 dB以上。

5 結論

該系統主要器件包括AD6645、EP2S60,其中AD6654實現ADC,EP2S60負責系統控制、通信、算法實現,最終來實現了信道化接收功能。因此,該系統具有高度的靈活性和很強的通用性,可通過軟件的重載或升級完成不同指標要求、不同模式的系統結構。在多板連接時,可以構成一個更大的陣列系統,可以用于DOA和DBF。

評論