利用FPGA實現(xiàn)的任意波形發(fā)生器的研究設(shè)計

1.3 雙口RAM設(shè)計

在設(shè)計波形存取電路時,首先應(yīng)確定波形RAM的深度和字長。波形RAM的深度和字長與很多因素有關(guān)系。存儲器內(nèi)部存儲的是一個或N個整周期的標(biāo)準(zhǔn)波形數(shù)據(jù),存儲器容量越大,存儲的被采樣波形點數(shù)就越多,采樣效果就越好。存儲器的讀取速度是產(chǎn)生高頻波形的重要保證,讀取速度必須滿足相位累加器的累加速度,這樣才能保證直接數(shù)字合成過程的正常進(jìn)行。同時,為了保證整個速度的同步性,選用一種同步RAM也是很必要的。

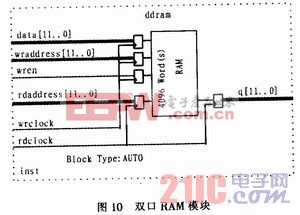

首先要確定波形RAM的深度和字長,由于任意波形發(fā)生器設(shè)計中選擇的DAC的字長是12位,很明顯波形RAM的字長也應(yīng)該是12位;由于選擇的地址線位數(shù)為12位(即相位累加器輸出的高12位),尋址空間為4 K(4 096)個單元,即RAM存儲空間應(yīng)為4 096x12 bit=49 152 bits,由于本設(shè)計所選擇的FPGA內(nèi)部RAM最大可配置為119 808 bits,完全可以滿足49 152 bits的RAM空間設(shè)計。所以波形RAM設(shè)計為字長12位,地址線12位。針對任意波形發(fā)生器與普通DDS的不同,波形RAM的設(shè)計主要要求RAM具有讀寫兩個端口,這樣可以通過兩套地址系統(tǒng),方便地進(jìn)行RAM內(nèi)容更新,即對RAM的寫操作;波形幅度量化數(shù)據(jù)的輸出,即對RAM的讀操作。結(jié)合ALTERA公司FPGA的特點,選擇了EP2C5F256C6這個芯片內(nèi)部的雙口RAM來實現(xiàn)這個功能,如圖10所示。

芯片內(nèi)部的雙口RAM具有讀地址和寫地址兩組地址線,數(shù)據(jù)線也分成了讀數(shù)據(jù)線和寫數(shù)據(jù)線兩組。這樣波形RAM的設(shè)計就非常簡單了,將寫數(shù)據(jù)線、寫地址線和單片機(jī)的數(shù)據(jù)線、地址線相連,用單片機(jī)更新RAM中的數(shù)據(jù);將讀地址線和讀數(shù)據(jù)線分別與相位累加器的輸出和DAC的數(shù)據(jù)輸入相連,讀數(shù)據(jù)線上即輸出了波形幅度量化數(shù)據(jù)。

2 結(jié)束語

本文詳細(xì)闡述了產(chǎn)生任意波形數(shù)據(jù)和基于FPGA的硬件設(shè)計部分,以QuartusⅡ8.O軟件平臺作為開發(fā)工具,選用CycloneII系列的EP2C5-F256C6 FPGA芯片實現(xiàn)DDS結(jié)構(gòu)中的數(shù)字部分,其中相位累加器是DDS的核心部件,重點闡述了相位累加器部分的設(shè)計,采用8級流水線結(jié)構(gòu)借助前5級的超前進(jìn)位模塊,編譯的最高工作頻率,由317.97 MHz提高到336.7 MHz,采用此種設(shè)計方法,節(jié)約了成本,縮短了開發(fā)周期,具有可行性。

評論