利用FPGA實現的任意波形發生器的研究設計

下面就將前5級采用超前進位加法器的32位累加器和宏模塊中調用的4位全加器組成的32位相位累加器性能進行比較。

普通流水線累加器的模塊是由4位D觸發器,5位D觸發器和4位全加器作為基本元件,采用原理圖輸入的方法設計FPGA的流水線累加器。該模塊的設計參照流水線累加器結構進行,不同之處在于:由于相位累加器只用高位尋址,所以低位上為了和高位結果同時輸出而做延時作用的D觸發器件均被去掉了。這樣做的結果是,相位累加器輸出的低20位會因為提前輸出而混亂,但是由于高12位的輸出一定是正確的,這樣做既節省了資源,對結果又沒有任何影響。仿真結果證明假如不用流水線結構,32 bit相位累加器工作頻率最高達到約25 MHz。消耗的資源是82個LEs,而用了8級流水線結構后,編譯工作頻率最高達到了約317.79 MHz,資源消耗為186個LEs。可見在資源上的消耗換來了在性能上的極大提高。

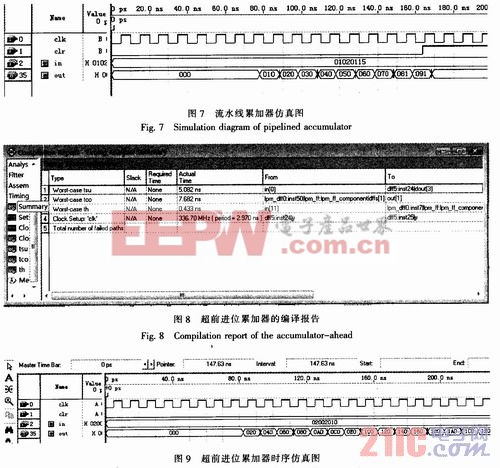

流水線累加器的時序仿真如圖7所示:可以看出當輸入數據確定后,輸出結果要經過8個時鐘周期的延時后輸出,這是因為采用了8級流水結構。采用多少級流水結構,輸出就會延時多少個周期。同時也說明,對于輸入數據切換來說,該系統會有8個時鐘周期的延時,這是累加器采用流水線結構所不可避免的后果。事實上目前許多DDS專用芯片由于也采用流水線結構,所以本身也存在這樣的問題。由于8個時鐘周期的延時與系統時鐘相比,實際上還是很小的,在一般的應用場合下也是可以接受的。由于輸出的低20位未用,被省略了,只用了輸出的高12位,所以仿真波形中只有高12位的輸出結果。從輸出結果來看,高12位的輸出值是沒有錯誤的,與設計思想吻合。

下面介紹超進位流水線累加器的構成,比較流水線累加器內部結構圖和超前進位加法器的32位相位累加器的結構圖,可以看出兩個圖的區別,經過編譯以后的報告如圖8所示,可以看出經過改進后,編譯的最大工作頻率提高到了336.7 MHz。比單純的流水線累加器提高了將近20 MHz。

圖9是其時序仿真圖,從圖上可以看出,其值完全和功能仿真一致。

評論